Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:57.

- Pēdējoreiz modificēts 2025-01-23 14:59.

Bienvenue dans notre projet Autotune

Notre équipe va vous présenter la réalisation de ce projet. Notre équipe est composée de 3 élèves ingénieurs de Polytech Sorbonne en EISE4 (4ème année du cycle ingénieur en électronique informatique systèmes embarqués).

Notre projet ir aprīkots ar vienu un to pašu mikrouzņēmumu, kā arī parfimēriju un līdzdalību FFT datorā. Ir iespējams mainīt modifikatoru, izmantojot audio skaņu un skaļumu.

C'est parti pour les explications !!

1. darbība. Komponentu izmantošana

- Karte DEO-Nano-SoC

- Baterijas 2 izeja - 5V2A

- Mikro

- Haut Parleur 8 omi

- Reģistrētājs: MAX660

- Capteur IR: GP2Y0E02A

- Audio pastiprinātājs: LM386N-1/NOPB

- DAC: MCP4821-E/P

- Diode: 1N4148

- Pārejas: LND150N3-G / N-FET

- 2 AOP: TL081C

- Rezistences

- Kondensatori

- Wi -Fi: ESP8266EX

- 4 slēdži

- 3 Leds de couleurs

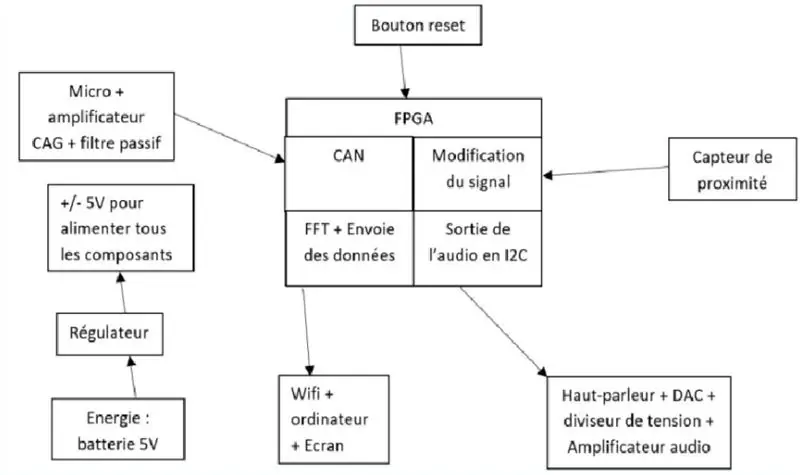

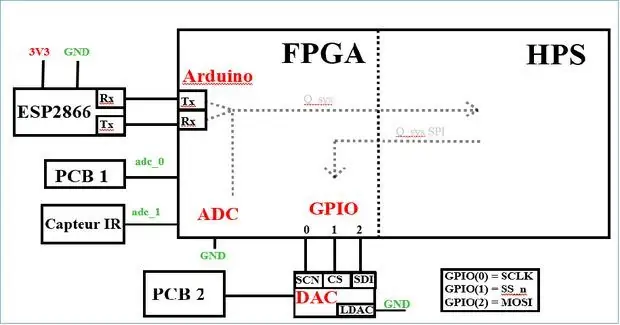

2. solis: arhitektūra

Voici ci-dessus notre schéma bloc représentant l'architecture de notre projet Autotune.

Comme vous pouvez le voir, notre projet va pouvoir capter un son à l'aide du micro dont le signal analogique capté sera converti en un signal numberumer dont dont l'ADC est intégré dans la carte FPGA. Puis le signal sera modifié selon nos effets choisis à l'aide d'un capteur de proximité et des switchs. Noslēdziet, mainiet signālu modifikāciju, pārtrauciet la carte sera reconverti un signālu analogique and sera transmise à travers le haut parleur.

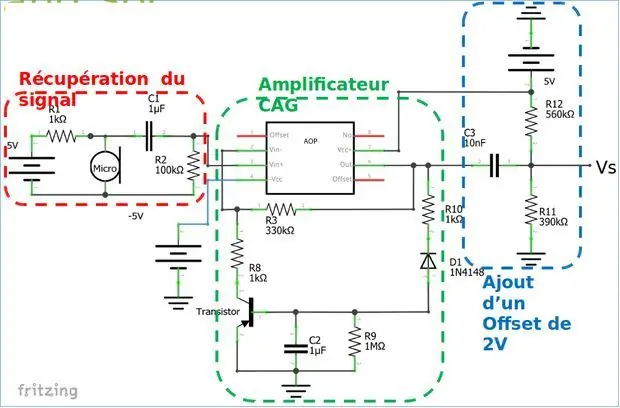

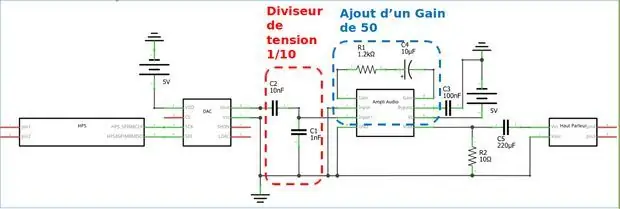

3. solis: Partie Analogique

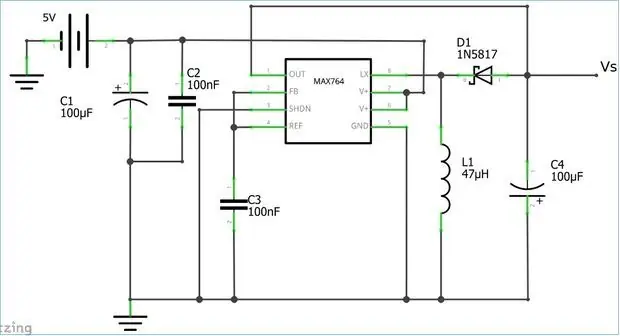

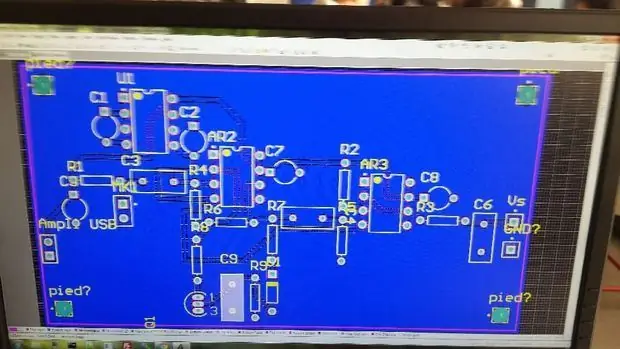

Notre partie analogie ir divu shēmu kompozīcija:

Un premier circuit qui reprèsera la partie micro, qui sera branché vai CAN de la carte FPGA, composie d'un amplificateur de gain and d filtr passif après avoir récupérer le signal.

Un deuxieme circuit qui repésentera la partie haut parleur, qui sera branchà à la sortie de la carte FPGA, composite du DAC, d'un diviseur de feszülts and d'un amplificateur audio.

Le troisième schéma est celui du régulateur produisant du -5V pour alimenter tous les composants.

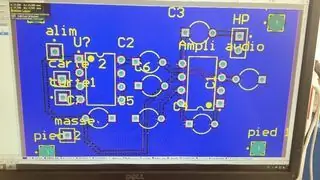

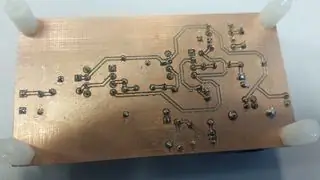

4. solis: PCB nospiedums

Uzturēšana, nous allons créer nos PCB afin de les imprimer et de les relier!

A l'aide du logiciel Alitum, nous avons pu creer deux PCB, c'est à dire la partie micro et haut parleur. Vietnes korespondents vai pasniedzējs Altium qui peut kindement vous aider!

5. solis: Partie Numérique

Après avoir imprimer vos PCB, vous pouvez enfin brancher le tout à la carte FPGA!

Pour partie numérique, nous avons créer un code C qui est séparé en deux en utilisant un thread. D'un coté, on récupère le signal on le modifie et on l'envoie vers le DAC en spi. D'un deuxième côté, par aprēķinu la fft et on envoie le résultat par wifi. Cette séparation permet d'éviter les ralentissements sur la première partie.

Izmantojot Qsys et quartus, ielejiet atzarojumu ar HPS avec les différents komponenti. Izmantojiet notamment une IP SPI ievietot komunikācijas avec le dac et une IP UART ievietot komunikācijas avec la carte wifi.

6. darbība: Le Code

Voici le lien où nous avons récuperé le code pour faire la fft.

Izmantojot kodu, ielejiet kalkulatoru:

// Création de la configuration et des buffers in et out pour s (t) et S (f) const kiss_fft_cfg config = kiss_fft_alloc (NFFT, 0, NULL, NULL);

kiss_fft_cpx*in = (kiss_fft_cpx*) malloc (NFFT*sizeof (kiss_fft_cpx)); kiss_fft_cpx*out = (kiss_fft_cpx*) malloc (NFFT*sizeof (kiss_fft_cpx));

par (j = 0; j <NFFT; j ++) {Value = *h2p_lw_adc_addr; // recupère la valeur provenant du pcb du microin [j].r = Value-2000.0; // pensijā l'offset de cette valeurfor (i = 0; i <2100; i ++) {} // visit un temps bien précis pour avoir une fréquence d’échantillonnage connue}

// FFT depuis aprēķins vers outkiss_fft (config, in, out); bzero (C_val, 110); // remet à zero le tableau qui nous sert de buffer que l'on va envoyer par wififor (t = 0; t <(NFFT/4); t ++) {// pour limiter la taille du buffer on limite la sortie de la fft à des valeurs entre 0 et 9 tmp_log = 20*(log (abs (out [t].r/1000.0)))*9;

tmp_log = tmp_log/50; ja (tmp_log <0) {tmp_log = 0; } ja (tmp_log> 9) {tmp_log = 9; } sprintf (tmp_val, "%d", tmp_log); strcat (C_val, tmp_val); // ajoute au buffer la nouvelle valeur

} send_wifir (C_val); // envoi le buffer par wifi

fonction send wifir:

void send_wifir (char* com_AT) {int num, z; par (z = 0; z <22000000; z ++) {} par (num = 0; num <(int) strlen (com_AT); num ++) { *(h2p_lw_rs232_addr) = com_AT [numurs]; }}

Izmantojiet inicializējošo la carte wifi, lai izmantotu kodu:

send_wifi ("AT+RST / r / n"); // demande de reset à la cartesleep (3); // apmeklēt qu'elle resetsend_wifi ("AT+CWMODE = 3 / n / r"); // izvēlieties le mode de la cartesend_wifi ("AT+CWJAP = \" wifiNom / ", \" MotDePasse / "\ r / n"); // on lui demande de se connecter au wifisleep (15); // on visit qu'elle se connectesend_wifi ("AT+CIPSTART = \" UDP / ", \" 192.168.43.110 / ", 32003 / r / n"); // On lui demande de se connecter en udp avec le serveur ouvert sur un autre ordinateursleep (3); // apmeklēt la connectxionsend_wifi ("AT+CIPMODE = 1 / r / n"); // on se met en mode envoie en turpina miega (3); send_wifi ("AT+CIPSEND / r / n"); // sāciet pārraidi

fonction sūtīt wifi:

void send_wifi (char * com_AT) {int num, z; for (num = 0; num <(int) strlen (com_AT); num ++) { * (h2p_lw_rs232_addr) = com_AT [numurs]; par (z = 0; z <2500000; z ++) {}}}

Servisa kods:

affichage de la fft:

int i, j, vērtība = 0; sistēma ("skaidrs");

par (i = 0; i <41; i ++) {ja (i <40) {par (j = 0; j <BUFSIZE; j ++) {ja (tabula [j]*4> (40 - i)) {ja (tabula [j]*4> 35) printf (RED "|" RESET); cits if (tabula [j]*4> 28) printf (L_RED "|" RESET); cits if (tabula [j]*4> 21) printf (YEL "|" RESET); cits if (tabula [j]*4> 14) printf (L_YEL "|" RESET); cits if (tabula [j]*4> 7) printf (L_GRN "|" RESET); else printf (GRN "|" RESET); } cits printf (""); } printf ("\ n"); } cits {printf ("0Hz 2.5Hz 5Hz 7.5kHz 10kHz / n"); /*par (j = 0; j <(BUFSIZE/2); j ++)

Ieteicams:

Mobilās pilnas uzlādes automātiskā izslēgšanās: 20 soļi

Mobilās pilnas uzlādes automātiskā izslēgšanās: mobilā tālruņa uzlādes pārtraukums automātiski, kad tas ir pilnībā uzlādēts. Neuztraucieties par akumulatora darbības laiku, pat ja to būtu atstājis nakti. Mobilos tālruņus darbina baterijas. Lai gan baterijas ir ērti lietojamas, to lietošanai ir nepieciešami arī daži piesardzības pasākumi. A ma

Automātiska suņu barotava !!: 4 soļi

Automātiska suņu barotava !!: Viegli, izpalīdzīgi un veselīgi

Automātiska augu laistīšanas sistēma, izmantojot mikro: bits: 8 soļi (ar attēliem)

Automātiskā augu laistīšanas sistēma, izmantojot mikro: bitu: Šajā pamācībā es jums parādīšu, kā izveidot automātisku augu laistīšanas sistēmu, izmantojot Micro: bit un dažas citas mazas elektroniskas sastāvdaļas. Micro: bit izmanto mitruma sensoru lai uzraudzītu mitruma līmeni auga augsnē un

Automātiska augu laistīšanas sistēma: 4 soļi

Automātiskā augu laistīšanas sistēma: Lūk, kā es izveidoju savu automātisko augu laistīšanas sistēmu

Golfa spēles Executive Par 3 automātiskā vērtēšana: 12 soļi (ar attēliem)

Automātiskā vērtēšana Executive Par 3 golfa spēlei: es nesen ievietoju pamācību par jautras, pārnēsājamas spēles izveidi, kuru var spēlēt gan iekšpusē, gan ārpus tās. To sauc par “Executive Par 3 golfa spēli”. Es izveidoju rezultātu kartītes kopiju, lai ierakstītu katra spēlētāja rezultātu par 9 “caurumiem”. Kā