Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:51.

- Pēdējoreiz modificēts 2025-01-23 14:59.

JDM ir populārs PIC programmētājs, jo tas izmanto seriālo portu, minimālu komponentu skaitu un neprasa barošanu. Bet tur ir neskaidrības, ar daudzām programmētāju variācijām tīklā, kuras no tām darbojas ar kādiem PIC? Šajā “pamācībā” mēs pārbaudījām JDM, un es demonstrēju, kā simulēt ķēdi, izmantojot Spice, kas atbildēs uz visiem jūsu jautājumiem!

Piegādes

LTspice, kuru var lejupielādēt no analogām ierīcēm šeit.

Šeit jums ir nepieciešami arī JDM shēmas faili.

1. darbība. Sērijas porta prasības

JDM nepieciešams seriālais ports, kas atbilst EIA232 specifikācijai, ideālā gadījumā ar +12/-12 sprieguma līmeņiem.

Saskaņā ar Texas Instruments Line Driver MC1488 datu lapu (3. attēls)

Izejas pretestība = 4V/8mA = 500 omi.

Īssavienojuma strāvas ierobežojums = 12 mV, bez laika ierobežojuma - nav bojājumu mikroshēmai.

Ieteicamā līnijas uztvērēja ieejas pretestība = 3k līdz 7k omi.

Vecāku galddatoru seriālie porti izmanto +12v/-12V, kas atbilst šai prasībai.

Jaunāko klēpjdatoru seriālajos portos tiek izmantots zemāks spriegums. JDM var darboties vai nedarboties - atbilde ir sarežģītāka.

2. darbība: PIC programmēšanas prasības

Informācija par PIC programmēšanas prasībām tiek iegūta no mikroshēmas. Iepriekš minētais attiecas uz tipisku ierīci.

3. darbība: JDM specifikācija

Vai sākotnējā JDM tīmekļa vietne laika gaitā ir pazudusi? Tas liek mums uzminēt, ko dizainers sākotnēji bija paredzējis specifikācijai.

- Nodrošiniet VDD = 5V un līdz IDD = maksimums 2mA (versijai "ligzdā")

- Nodrošiniet VHH = 13V un maksimāli līdz IHH = 0.2mA.

- MCLR Pieauguma laiks tVHHR = maks. 1uS.

- ICSP versijai jāspēj zemā līmenī izvilkt MCLR pret 22k pievilkšanos uz mērķi.

4. darbība. Ķēdes apraksts

Attēls JDM1 ir balstīts uz “standarta” JDM shēmu, kas ņemta no PICPgm tīmekļa vietnes. Šis ir “PIC in Socket” programmētājs, kurā PIC saņem enerģiju no TX un RTS tapām. Sākotnējo diagrammu bija grūti saprast, tāpēc esmu to pārzīmējis, izmantojot parasto strāvas plūsmas metodi no augšas uz leju. Un es esmu pievienojis LED indikatorus “RESET”, “PROG” un “RTS”, kas nepieciešami būvniecības un testēšanas laikā. Cerams, ka tiem nav nekādas kaitīgas ietekmes uz uzvedību.

Parastā shēmas konstrukcija ir kopīga visiem iemesliem, taču JDM galvenā iezīme ir tā, ka seriālā porta zeme (GND) ir savienota ar VDD. Tas rada neskaidrības, jo seriālā porta signālus mēra attiecībā pret GND, PIC signālus attiecībā pret loģisko zemi (VSS).

Kad TX paaugstinās, Q1 darbojas kā divas uz priekšu novirzītas diodes. (Q1 kolektors nav pretēji novirzīts kā parastajā tranzistora darbībā). Q1 kolektors uzlādē C2, ko Zener (D3) piestiprina pie VDD+8V. Q1 emitētājs nodrošina 13V uz MCLR programmēšanas/verifikācijas režīmam.

Kad TX samazinās, kondensators C3 tiek uzlādēts caur D1, un VSS tiek piestiprināts pie VDD-5V ar zener (D5). Arī TX ir piestiprināts pie (VSS-0.6) ar D1. Q1 ir izslēgts, C1 saglabā maksu par nākamo programmēšanas impulsu. MCLR pie 0V piestiprina D2, tāpēc PIC tagad ir atiestatīts.

Ja RTS ir augsts, pulkstenis tiek pārsūtīts uz PGC. D4 skava PGC pie augsta VDD loģikas. Kad RTS ir zems, kondensators C3 tiek uzlādēts caur D6, un VSS ar zener (D5) piestiprina pie VDD-5V. D6 saspiež PGC pie VSS vai loģikas 0.

Programmēšanas laikā DTR nosūtītie dati tiek nolasīti PGD, ko PIC konfigurē kā ievadi. Ja DTR ir augsts, Q2 darbojas kā “emitētāja sekotājs”, un PGD spriegums ir aptuveni (VDD-0,6) vai loģika 1. Ja DTR ir zems, Q2 darbojas kā slikts tranzistors (emitētāja un kolektora tapas ir apgrieztas). Q2 pazemina PGD zemu, ko D7 saspiež pie VSS vai loģikas 0.

Pārbaudes laikā PIC konfigurē PGD kā izeju datu nosūtīšanai uz seriālo portu. DTR jābūt iestatītam augstam, un dati tiek nolasīti CTS. Ja PGD izeja ir augsta, Q2 ir izslēgts, CTS = DTR = +12V. Ja PGD izvade ir zema, Q2 ir ieslēgts. Q2 kolektors ņem strāvu (12V+5V)/(1k+1k5) = 7mA no DTR un velk CTS zemu līdz VSS.

5. solis: sagatavojieties simulācijai

Lejupielādējiet LT spice, saglabājiet un atveriet šeit sniegtos ķēdes failus (*.asc). Lai simulētu ķēdi, mums tai jāpiešķir daži ievadi, pēc tam “jāseko” izejām. V1, V2 V3 simulē 12V seriālo portu ar izejas pretestību R11, R12, R13.

- V1 ģenerē 2 programmas impulsus TX no 0,5 ms līdz 4,5 ms

- V2 ģenerē datu impulsu sēriju DTR no 1,5 līdz 4,5 ms

- V3 ģenerē pulksteņa impulsu pārrāvumu RTS no 0,5 līdz 3,5 ms

Visi komponenti V4, X1, R15 un R16 ir simulācijas sastāvdaļa.

- V4 ģenerē 2 impulsus no 2,5 līdz 4,5 ms datu pārbaudei.

- Džemperis X1 simulē izeju uz PGD.

- R15, R16 simulē PIC “ielādi” VDD un MCLR.

6. darbība: izmaiņas ICSP

Attēlā JDM3 ir parādīta “ķēdes” programmēšanas versija. Izmaiņas no oriģināla ir

- Nomainiet ZIF ligzdu ar ICSP savienotāju.

- PIC tagad tiek darbināts ar barošanu mērķa ķēdei (V5).

- Noņemiet 5V zener (D5).

- Mazais 100pF kondensators (C4) mērķa ķēdē tiek pārvietots blakus PIC.

- Ja iespējams, gaismas diodes ņem strāvas padevi no shēmas plates.

- Mērķa ķēdē ir nepieciešams MCLR pievilkšanas rezistors (R10) un diode (D10).

- BRĪDINĀJUMS Mērķa plāksnei jābūt “peldošai” barošanai, ideālā gadījumā - akumulatoram.

- Nepievienojiet mērķa zemi (VSS) datora/datora iezemējumam, pievienojot citus datora portus vienlaikus ar JDM.

Pēc JDM1 simulācijas kļuva redzama problēma ar ilgu uzlādes laiku C2. Pēc Fruttenboel lasīšanas šķiet, ka C2 un Q1 tika pievienoti oriģinālam kā modifikācija. Es nevaru iedomāties, ko C2 un Q1 paredzēts darīt, izņemot problēmu radīšanu. Tātad attiecībā uz JDM4 mēs atgriežamies pie Fruttenboel vecākā dizaina, kas ir vienkāršs un saprotams. D1 un D3/LED2 skava MCLR starp VSS un VDD+8V. R1 vērtība ir samazināta līdz 3 k3, kas ir pietiekami, lai apgaismotu LED2 pie 12 V sprieguma.

JDM4 ir paredzēts darbam arī ar vājākiem seriālajiem portiem. Kad TX ir augsts (+9V), TX strāvas avots = (9-8)/(1k +3k3) = 0.2ma, tieši tik daudz, lai paceltu MCLR augstu, lai gan nepietiek, lai apgaismotu LED2. Kad TX samazinās (aptuveni -7V), TX strāvas slāpētājs = (9-7)/1k = 2mA. LED1 strāva = (7-2 LED)/(2k7) = 1,8 mA. MCLR nolaišanas strāva = 7-5,5/3k3 = 0,5 mA.

Šī shēma ir arī pārbaudīta (JDM5 simulācija), lai noskaidrotu, kas notiek ar seriālajiem portiem vismaz +/- 7V, ja nepietiek sprieguma, lai uzturētu VHH = 13V. C1 mērķis tagad kļūst skaidrs, C1 rada īsu +ve palielinājumu MCLR, 33us smaile uz TX augšupejošās malas, pietiekami ilgs, lai PIC varētu ieslēgt programmēšanas režīmu, iespējams? Bet noņemiet džemperi X2 (atspējojiet LED1), jo nav pietiekami daudz strāvas, lai samazinātu MCLR un apgaismotu LED1 kopā. Kad TX kļūst zems, TX strāvas slāpētājs = (7V-5,5 V)/(1k+3k3) = 0,3 mA, kas ir pietiekami, lai MCLR zemu pievilktu pret pievilkšanas R10.

7. darbība. Simulācijas rezultāti

Lai skatītu grafiskos failus, labāk ar peles labo pogu noklikšķiniet uz zemāk esošajām saitēm un pēc tam atlasiet “Atvērt saiti jaunā cilnē”.

1. simulācija: MCLR, VSS un RTS izsekošana sākotnējam JDM1. Uzreiz ir redzams 1., 2. un 3. novērojums.

2. simulācija: MCLR un VSS izsekošana un modificēta JDM2 RTS, kas novērš iepriekšējās problēmas.

3. simulācija: PGD, VSS un PGC izsekošana JDM2 datu nosūtīšanai programmas režīmā. 4. novērojums pie 3,5 mS.

4. simulācija: PGD, VSS un CTS izsekošana JDM2 verifikācijas režīmā (ievietots džemperis X1). labi

5. simulācija: MCLR, VSS, PGD un PGC izsekošana JDM3. ICSP, izmantojot strāvas padevi no ķēdes, atrisina daudzas problēmas.

6. simulācija: MCLR, VSS, PGD un PGC izsekošana JDM4 ar +/- 9V seriālo portu. MCLR nekavējoties paaugstinās, pilnībā darbojoties.

7. simulācija: MCLR, VSS un TX pēdas JDM5 ar +/- 7V seriālo portu un džemperi X2. C1 rada +ve palielinājumu (smaile) uz MCLR augšupejošās malas, kas ir gandrīz pietiekami, lai pārspiestu MCLR virs TX līdz 13 V.

8. solis: Secinājumi

Spice patiešām labi atklāj ķēdes darbības “slēptos noslēpumus”. Acīmredzot JDM ķēde darbojas un ir saderīga ar daudzām PIC mikroshēmām, taču šādi novērojumi atklāj iespējamos ierobežojumus/saderības problēmas/kļūdas?

- Ilgs MCLR pacelšanās laiks, kamēr C2 tiek uzlādēts VPP pirmajā TX impulsā. Neatbilst specifikācijai 3.

- Sērijas ports uzlādē C2, kad TX ir augsts un RTS - zems. Bet RTS ir arī uzdevums uzlādēt C3. Ja abi notiek vienlaicīgi, tas rada lielāku slodzi RTS, līdz ar to C3 zaudē uzlādi (VSS palielinās) pēc 2 ms simulācijas laikā. Neatbilst specifikācijai 1.

- C3 zaudē uzlādi (VSS sāk pieaugt) pēc pulksteņa impulsu apstāšanās pie 3,5 ms.

- Kāds ir C2 mērķis, vai tas vispār ir vajadzīgs?

Risinājumi

- Jādomā, ka PICPgm izmanto programmatūru “aplis”. Tai ir jāpiemēro garš TX impulss, lai uzlādētu C2, un pēc tam jāievada programmēšanas režīms tikai pēc otrā TX impulsa? Simulācijai es samazināju C2 vērtību līdz 1uF, lai iegūtu pieauguma laiku 1 ms. Nav ideāls risinājums.

- Sadaliet C2 un C3, lai tie uzlādētos neatkarīgi. Viena neliela JDM2, C2 modifikācija ir atsauce uz GND, nevis VSS.

- Atrisināja JDM3. ICSP ir daudz uzticamāka, jo PIC baro mērķa ķēde.

- JDM4 atrisina 1. problēmu. Šis ir vienkāršs dizains, kas pilnībā novērš C2.

9. solis: un visbeidzot

Pudiņa pierādījums ir ēšana. Šis JDM darbojas, tāpēc turpiniet to izmantot.

Un mani ieteikumi ir šādi:

- izmantojiet JDM2 ligzdu programmēšanai un 12 V seriālajiem portiem,

- izmantojiet JDM4 ICSP programmētājam un seriālajiem portiem virs +/- 9V,

- izmantojiet JDM4 ar noņemtu džemperi X2 sērijveida portiem virs +/- 7V.

Atsauces:

Analog Devices LT garšviela

picpgm

Fruttenboel

Sekojiet citiem PIC projektiem viltīgajā stūrī

Ieteicams:

Elegoo Super iesāktais komplekts Uno R3 apskats: 4 soļi

Elegoo Super sākuma komplekts Uno R3 apskats: Pirms dažām dienām Elegoo nosūtīja man šo Super sākuma komplektu testēšanai. Tātad, redzēsim, kas ir iekšā. Atverot šo kompakto korpusu, mēs varam redzēt daudz lietas. Uz vāka ir rādītājs ar visām sastāvdaļām. Iekšpusē mums ir pateicības kartīte ar visiem

ESP -01 programmētāja uzlaušana - vienkāršākais :): 6 soļi

ESP-01 programmētāja uzlaušana-vienkāršākais :): Sveiki, ESPers! Šajā pamācībā es jums parādīšu vienkāršu uzlaušanu, lai izveidotu programmētāju modulim ESP-01 / ESP8266-01 / ES-01. Lielākā daļa no mums ir izmantojuši Arduino plati vai FTDI USB-TTL ierīces kā šī moduļa programmētāji. Abas metodes darbojas labi. Bet t

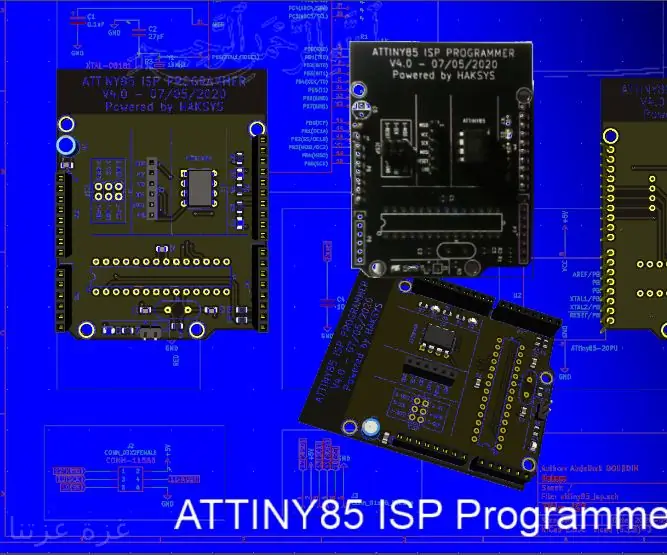

Vēl viens ATTINY85 ISP programmētāja vairogs Arduino: 8 soļi

Vēl viens ATTINY85 ISP programmētāja vairogs Arduino. Sērijas programmētājs & quot

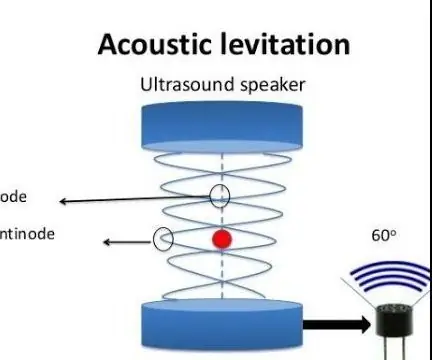

Akustiskā levitācija ar Arduino Uno soli pa solim (8 soļi): 8 soļi

Akustiskā levitācija ar Arduino Uno soli pa solim (8 soļi): ultraskaņas skaņas pārveidotāji L298N līdzstrāvas adaptera strāvas padeve ar vīriešu līdzstrāvas tapu Arduino UNOBreadboard un analogie porti koda konvertēšanai (C ++)

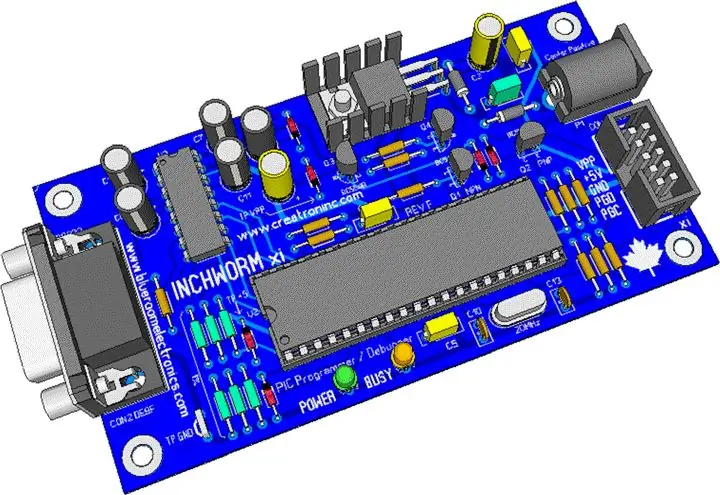

Inchworm ICD2 PIC programmētāja / atkļūdotāja izveide: 7 soļi

Inchworm ICD2 PIC programmētāja / atkļūdotāja izveide: šī pamācība ir ilustrēta pastaiga, veidojot ICD2 klonu, ko sauc par Inchworm. Tas ir vienkāršs komplekts, kas ļauj izveidot ar MPLAB ICD2 saderīgu programmētāju un atkļūdotāju. Ir daudz programmētāju, bet ļoti daži ietver