Satura rādītājs:

- 1. darbība. Bloķēt diagrammu

- 2. solis: darbības princips

- 3. darbība: loģikas ieviešana

- 4. solis: atrisiniet strupceļu

- 5. solis: ierīces konfigurācija - Matrix0 ķēde

- 6. darbība: ierīces konfigurācija - SPI pulksteņa loģika

- 7. darbība: ierīces konfigurācija - Matrix0 komponentu rekvizīti

- 8. darbība. Ierīces konfigurācija - Matrix1 ķēde

- 9. solis: ierīces konfigurācija - 3 bitu binārais skaitītājs

- 10. solis: ierīces konfigurācija - 3 bitu salīdzināšanas loģika

- 11. darbība. Ierīces konfigurācija - digitālā salīdzinājuma loģika un pagaidu reģistrs

- 12. solis: ierīces konfigurācija - Matrix1 komponentu rekvizīti

- 13. darbība. Rezultāti

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:53.

- Pēdējoreiz modificēts 2025-01-23 14:59.

Vadības sistēmas un saistītās ierīces darbojas ar vairākiem strāvas avotiem, piemēram, slīpuma līnijām vai baterijām, un tām ir jāseko augstākajai (vai zemākajai) līnijai no noteiktā komplekta.

Piemēram, slodzes pārslēgšanai sistēmā, kas darbojas ar vairākiem akumulatoriem, ir nepieciešams, lai sistēma uzraudzītu minimālo vai maksimālo spriegumu starp akumulatoru bloku (maks. Vai min. Atkarībā no konkrētā pārslēgšanas algoritma) un dinamiski novirzītu slodzi uz vispiemērotākais avots reālajā laikā. Lai pareizi uzlādētu, sistēmai, iespējams, būs īslaicīgi jāatvieno zemākā sprieguma akumulators.

Vēl viens piemērs ir mūsdienīga saules enerģijas sistēma, kurā katrs saules panelis ir aprīkots ar rotējošu rotācijas mehānismu un saules izsekošanas ķēdi (pēdējā sniedz informāciju par Saules stāvokli, lai orientētu paneli). Izmantojot informāciju par maksimālo spriegumu, katru saules paneļa pozīciju var precīzi noregulēt, pamatojoties uz virknes paneli, kas faktiski nodrošina augstāko izejas spriegumu, tādējādi panākot izcilu jaudas optimizācijas līmeni.

Ir vairāki dažādi komerciālo IC zīmoli (galvenokārt mikrokontrolleri), kas principā var ieviest maksimālā sprieguma sekotāju. Tomēr tie prasa programmēšanu un ir mazāk rentabli nekā jaukta signāla risinājums. Dialog GreenPAKTM dizaina papildināšana var pozitīvi ietekmēt dizaina pieejamību, izmēru un modularitāti. Šis dizains izmanto priekšrocības, integrējot gan analogās, gan digitālās shēmas vienā mikroshēmā.

Šajā pamācībā tiek ieviesta analogā priekšpuse un digitālā loģika, kas nepieciešama maksimālā (vai galu galā min) sprieguma meklētāja ieviešanai starp astoņiem atšķirīgiem avotiem.

Lai izveidotu 8 kanālu analogo maksimālā/min sprieguma monitoru, tiek izmantots SLG46620G.

Tālāk mēs aprakstījām nepieciešamās darbības, lai saprastu, kā risinājums ir ieprogrammēts, lai izveidotu 8 kanālu analogo maksimālā/min sprieguma monitoru. Tomēr, ja vēlaties tikai iegūt programmēšanas rezultātu, lejupielādējiet GreenPAK programmatūru, lai apskatītu jau pabeigto GreenPAK dizaina failu. Pievienojiet GreenPAK attīstības komplektu datoram un nospiediet programmu, lai izveidotu 8 kanālu analogo maksimālā/min sprieguma monitoru.

1. darbība. Bloķēt diagrammu

1. attēlā parādīta ieviestās sistēmas globālā diagramma.

Līdz 8 mainīga sprieguma avotu virkne ir multipleksēta un savienota ar GreenPAK ADC moduli, kas savienots ar pielāgotu iekšējo dizainu, kas spēj izvēlēties avotu ar augstāko spriegumu attiecībā pret citiem. Iekšējā loģika izvada šo informāciju attēlošanai vai turpmākai apstrādei.

Dizaina pamatā ir GreenPAK SLG46620G produkts, jo tajā ir iestrādāti visi lietojumprogrammai nepieciešamie analogie un digitālie bloki. Šajā ieviešanā masīvs tiek skenēts, izmantojot ADG508 analogo multipleksoru, ko tieši vada GreenPAK IC.

Izejas informācija ir 3 bitu ciparu skaitlis, kas atbilst sprieguma avota numuram pie maksimālā sprieguma. Tiešs veids, kā iegūt šo informāciju, ir rādīt numuru, izmantojot 7 segmentu displeju. To var viegli paveikt, sasaistot SLG46620G digitālo izvadi ar 7 segmentu displeja draiveri, piemēram, GreenPAK risinājumu, kas aprakstīts atsaucē, vai parasto 74LS47 IC.

Piedāvātā shēma meklē maksimālo spriegumu. Lai pārveidotu dizainu par minimālā sprieguma meklētāju, starp analogo multipleksoru un GreenPAK analogo ieeju jāpievieno vienkārša iepriekšējas sagatavošanas ķēde, atņemot multipleksora izeju no 1 V atskaites sprieguma.

2. solis: darbības princips

Dizaina mērķis ir izvēlēties avotu ar maksimālo spriegumu, tāpēc tiek veikta skenēšana visam masīvam, vienlaikus saglabājot pēdējo maksimālo vērtību un salīdzinot to ar nākamo ievades vērtību (kas pieder pie nākamā sprieguma avota skenēšanas laikā).

Turpmāk mēs norādīsim uz pilnīgu multipleksēšanas secību visās ieejās kā “skenēšanu” vai “cilpu”.

Divu vērtību salīdzinājums netiek veikts, izmantojot ACMP komponentus (tomēr ir pieejami SLG46620G), bet gan DCMP moduli, tiklīdz vērtības ir attiecīgi digitalizētas. Šī ir uzlabota un izsmalcināta tehnika, kas vispirms tika apskatīta atsaucē.

2. attēlā parādīts, kā SLG46620G ir veidots šim dizainam.

Analogais ieejas signāls iet uz ADC ieeju caur PGA komponentu ar iestatījumu Gain 1. Ir pieejami arī dažādi Gain iestatījumi, lai atrastu vislabāko atbilstību priekšējās daļas kondicionēšanas elektronikai, kas paredzēta ieejas sprieguma kartēšanai ar 0-1 V GreenPAK ADC moduļa klāsts.

ADC darbojas viena gala režīmā un pārveido analogo signālu 8 bitu digitālā kodā, kas pēc tam tiek pārsūtīts uz DCMP moduli. Digitālais kods tiek ievadīts arī SPI blokā, kas konfigurēts kā ADC/FSM buferis, kur var saglabāt digitālo kodu un nemainīsies, līdz nākamais impulss nonāks SPI CLK ievadē. Ņemiet vērā, ka speciāls loģikas bloks vada SPI CLK ievadi. Šo daļu mēs izmeklēsim vēlāk, jo tā ir “pamata” loģika, kas ir atbildīga par pareizu darbību. Jauns digitālais kods tiek saglabāts SPI modulī tikai tad, ja tas pieder faktiskajam maksimālajam ieejas spriegumam.

DCMP komponentu izmanto, lai salīdzinātu pašreizējos ADC datus ar pēdējo uzvarētāju (tas ir, pēdējais atrastais maksimums), kas tiek saglabāts SPI blokā. Tas ģenerēs impulsu pie OUT+ izejas, kad jaunie ADC dati būs lielāki par iepriekšējiem. Mēs izmantojam OUT+ signālu, lai atjauninātu SPI bloku ar jauno uzvarētāju.

Globālais pulksteņa signāls veicina ADC reklāmguvumus un vispārējo laiku. Kad konversija ir veikta, ADC INT izejas signāla impulsi tiek savlaicīgi saskaņoti ar ADC paralēlo datu izvadi. Mēs izmantojam INT izvadi arī, lai palielinātu 3 bitu bināro skaitītāju, ko Matrix1 ieviesa DFF, kas ir noderīgi trīs iemeslu dēļ:

1. Skaitītāja izejas līnijas adresē ārējo analogo multipleksoru, tādējādi kalpojot nākamajam ADC ieejas spriegumam;

2. Skaits tiek iesaldēts 3 bitu reģistrā (ieviests Matrix1), lai saglabātu pagaidu uzvarētāju skenēšanas laikā;

3. Skaits tiek atšifrēts, lai pēc skenēšanas pabeigšanas atjauninātu otru 3 bitu reģistru (ieviests Matrix0).

3. darbība: loģikas ieviešana

ADC modulis secīgi nenoteiktu laiku nodrošina konvertētus datus par visiem ieejas spriegumiem. Kad Multiplekseris ir adresēts 0b111 (decimālskaitlis 7), skaitītājs tiek noņemts līdz 0b000 (decimālskaitlis 0), tādējādi uzsākot jaunu ieejas sprieguma skenēšanu.

Skenēšanas laikā ADC INT izejas signāls tiek ģenerēts, ja ir derīga paralēlā datu izvade. Kad šis signāls pulsē, analogajam multiplekserim jāpārslēdzas uz nākamo ieeju, nodrošinot PGA atbilstošo spriegumu. Tāpēc ADC INT izeja ir tiešs pulksteņa signāls no 2. attēla 3 bitu binārā skaitītāja, kura 3 bitu paralēlās izejas vārds tieši adresē ārējo analogo multipleksoru (“V select” 1. attēlā).

Ļaujiet mums tagad atsaukties uz piemēru, kurā ieejas spriegumiem vajadzētu būt šādām attiecībām:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

3. attēlā parādīti galvenie signāli, kas saistīti ar maksimālo lēmumu pieņemšanas mehānismu.

Tā kā dati galu galā tiek reģistrēti SPI bufera reģistrā sinhroni ar INT impulsiem, pastāv salīdzināšanas logs, kurā SPI bufera saturs tiek salīdzināts ar nākamo ADC konversijas rezultātu. Šī īpašā laika rezultātā DCMP izejā tiek ģenerēti OUT+ impulsi. Mēs varam izmantot šos impulsus, lai ielādētu jaunas vērtības SPI bufera reģistrā.

Kā redzams no iepriekšējā attēla SPI bufera datu rindas, SPI reģistrā vienmēr ir vislielākā vērtība starp 8 ievadēm, un tas tiek atjaunināts tikai tad, ja DCMP modulis nosaka lielāku vērtību (atsaucoties uz DCMP) OUT+ diagrammas izvades līnija, trūkstošo impulsu dēļ V2 reģistrā paliek fiksēts, salīdzinot ar V5).

4. solis: atrisiniet strupceļu

Ja īstenotā loģika būtu tieši tāda, kā aprakstīts iepriekš, ir skaidrs, ka mēs nonāktu strupceļā: sistēma spēj noteikt tikai spriegumus, kas ir augstāki par spriegumu, kas atbilst SPI bufera reģistrā saglabātajam.

Tas ir spēkā arī gadījumā, ja šis spriegums samazināsies un tad cita ieeja, kas līdz šim ir zemāka, kļūst par augstāko: tā nekad netiks atklāta. Šī situācija ir labāk izskaidrota 4. attēlā, kur ir tikai 3 ieejas spriegumi. skaidrība.

2. iterācijas laikā V3 samazinās un V1 ir faktiskais maksimālais spriegums. Bet DCMP modulis nenodrošina impulsu, jo SPI bufera reģistrā saglabātie dati (kas atbilst 0,6 V) ir lielāki nekā V1 (0,4 V).

Pēc tam sistēma darbojas kā “absolūtais” maksimālais meklētājs un neatjaunina izvadi pareizi.

Jauks veids, kā pārvarēt šo problēmu, ir piespiest atkārtoti ielādēt datus SPI bufera reģistrā, kad sistēma pabeidz pilnu visu kanālu aptaujas ciklu.

Patiesībā, ja spriegums pie šīs ieejas joprojām ir visaugstākais, nekas nemainās un vadība turpinās droši (atsaucoties uz 4. attēlu iepriekš, tas ir gadījumā ar 0 un 1 cilpas atkārtojumiem). No otras puses, ja spriegums pie šīs ieejas nejauši pazeminās līdz vērtībai, kas ir mazāka par citu ieeju, tad vērtības atkārtota ielāde dod iespēju DCMP modulim radīt OUT+ impulsu, salīdzinot to ar jauno maksimālo vērtību (tā ir 2. un 3. cilpas atkārtojumu gadījums).

Lai pārvarētu problēmu, ir nepieciešama loģikas shēma. Tai jāģenerē pulksteņa signāls SPI komponentam, kad cilpa sasniedz faktisko maksimālo ievadi, tādējādi liekot atkārtoti ielādēt atjaunināto datu vārdu SPI bufera reģistrā. Tas tiks apspriests 7.2. Un 7.6. Sadaļā.

5. solis: ierīces konfigurācija - Matrix0 ķēde

SLG46620G ir divi matricas bloki, kā parādīts 2. attēlā. Turpmākajos attēlos ir parādītas attiecīgās ierīces konfigurācijas.

Ķēdes augšējā daļa ir “cilpas reģistrs”, kas realizēts ar 3 DFF (DFF0, DFF1 un DFF2). Pēc katras ievades multipleksora cilpas tiek atsvaidzināts nosūtīt 7 segmentu displeja draiverim “uzvarētāja” bināro numuru, tas ir, ievadi ar augstāko spriegumu pēdējā skenēšanas laikā. Gan pulkstenis uz DFF, gan dati nāk no Matrix1 ieviestās loģikas, attiecīgi caur portu P12, P13, P14 un P15.

Apakšējā daļa ir analogā priekšējā daļa ar ieeju 8. tapā un PGA ar pastiprinājumu x1. ADC INT izeja iet gan uz SPI pulksteņa loģiku, gan uz Matrix1, izmantojot portu P0, kur tā kalpos kā pulksteņa signāls realizētajam skaitītājam.

ADC un SPI paralēlie datu izvadi ir attiecīgi marķēti ar NET11 un NET15, lai tie būtu savienoti ar DCMP komponentu Matrix1.

6. darbība: ierīces konfigurācija - SPI pulksteņa loģika

Kā jau iepriekš norādīts sadaļā “Loģikas ieviešana”, SPI bufera reģistrs tiek atjaunināts katru reizi, kad salīdzinājums starp faktisko saglabāto vērtību un jaunajiem ADC reklāmguvumu datiem ģenerē impulsu DCMP OUT+ izejā.

Signāla integritāte tiek nodrošināta, ja šis signāls ir AND-ed ar ADC INT izeju. Tas ļauj izvairīties no pīķa un viltus iedarbināšanas.

Mēs arī uzsvērām, ka, lai izlaistu strupceļa situācijas, SPI buferis ir jāatjaunina, kad cikls sasniedz faktiskos uzvarētāju datus.

Pēc tam spēlē ir trīs signāli pareizai SPI pulksteņrādīšanai:

1. ADC INT izeja (LUT0-IN1)

2. DCMP OUT+ izeja (LUT0-IN0 caur portu P10)

3. Skaits ir vienāds ar fiksatora signālu (LUT0-IN2, izmantojot portu P11)

Pirmie divi ir UN-red, un abi OR-ed ar pēdējo LUT0, kura ieviešana ir konfigurēta kā 6. attēlā.

7. darbība: ierīces konfigurācija - Matrix0 komponentu rekvizīti

Attēlos 7-10 ir parādīti atlikušie komponentu rekvizītu logi, kas pieder Matrix0.

8. darbība. Ierīces konfigurācija - Matrix1 ķēde

9. solis: ierīces konfigurācija - 3 bitu binārais skaitītājs

Ķēdes augšējā daļā ir loģikas elementi, galvenokārt 3 bitu binārais skaitītājs, kas pulksteņots ar ADC INT izeju, kā jau tika apspriests. Šis skaitītājs ir ieviests ar diezgan “standarta” shēmu, kas parādīta 12. attēlā.

Šis skaitītājs ir realizēts mūsu dizainā, izmantojot flip-flops DFF9, DFF10, DFF11 un INV1, LUT4, LUT8. DFF9 izeja ir LSB, bet DFF11 ir MSB, kā parādīts 13. attēlā.

LUT4 ir konfigurēts kā XOR, bet LUT8 izpilda 12. attēla AND-XOR loģiku.

Skaitītāja izejas nonāk pie trim digitālās izejas tapām, lai adresētu ārējo analogo multipleksoru.

Kad skenēšana ir pabeigta, LUT10 dekodē skaitītāja kodu un padevi impulsu Matrix0, izmantojot DLY8 un portu P12. Tas tiek vienkārši paveikts, AND ierakstot skaitītāja izejas, tādējādi dekodējot skaitli 7 dec (0b111 binārais, cikla beigas).

10. solis: ierīces konfigurācija - 3 bitu salīdzināšanas loģika

15. attēlā parādīta ķēde, ko izmanto, lai noteiktu, kad cilpa atkārtojas pašreizējā “uzvarētāja” adresē. Šajā gadījumā, kā jau tika apspriests, digitālajam impulsam vajadzētu piespiest atkārtoti ielādēt pašreizējo ADC rezultātu, lai atrisinātu iespējamo strupceļa situāciju.

Uzvarētāja adrese tiek saglabāta Matrix1 pagaidu reģistrā (skatīt zemāk), bet pašreizējo adresi izvada binārais skaitītājs.

XNOR vārti nodrošina patiesu (loģisko 1 vai “augstu”) izvadi, ja abas ieejas ir vienādas. UN šī signāla ievadīšana visiem bitiem (LUT9) dod mums impulsu, ja abi binārie kodi ir vienādi. Sīkāka informācija par XOR vārtiem kā paritātes pārbaudītāju ir atrodama sadaļā Atsauce.

Signāls “Counter-equals-Latch” tiek nosūtīts uz Matrix0, izmantojot portu P11.

11. darbība. Ierīces konfigurācija - digitālā salīdzinājuma loģika un pagaidu reģistrs

11. attēla apakšējā daļā (iezīmēts 16. attēlā) ir parādīts DCMP bloks, šī dizaina lēmuma pieņemšanas daļa.

DFF6, 7 un 8 veido 3 bitu reģistru, lai saglabātu pagaidu ievades numuru “uzvarētājs”, kamēr cikls darbojas. Ievads Flip-Flops ir 3 bitu binārā skaitītāja izejas, kā redzams 11. attēla globālajā Matrix1 ķēdē, šeit skaidrības labad tās izlaistas.

Šī reģistra izejas nevar tieši vadīt 7 segmentu displeju, jo šeit saglabātā vērtība skenēšanas laikā mainās, un tā būtu jāuzskata par “derīgu” tikai pašas skenēšanas beigās.

Šī iemesla dēļ pagaidu reģistra izejas savienojas ar Matrix0 cilpas reģistru, izmantojot starpmatricas portus P13, P14 un P15.

Ir svarīgi novērot 16. attēlā, ka pagaidu reģistrs tiek pulksteņots ar DCMP OUT+ izeju, kad ADC-SPI reģistru salīdzināšanas rezultātā tiek atrasts jauns maks.

Tas pats OUT+ signāls tiek nodots Matrix0, SPI CLK Logic, izmantojot portu P10.

12. solis: ierīces konfigurācija - Matrix1 komponentu rekvizīti

Attēlos 17-19 ir parādīti Matrix1 komponentu īpašību logi.

13. darbība. Rezultāti

Lai pārbaudītu ieviešanu, ir izveidots novērtēšanas paneļa prototips, kurā 8 analogos ieejas spriegumus iegūst virkne rezistoru dalītāju ar TrimPots (kā parādīts 20. attēlā).

Izmantotais multipleksors ir ADG508, daļa, kas var darboties ar vienu barošanu (12 V).

7 segmentu displeja draiveris ir 74LS47. Tas atšifrē paralēlo ievades vārdu un tieši vada 7-segmentu displeju ar parasto anodu.

Novērtēšanas panelim ir 2x10 taisna leņķa savienotājs, lai to varētu tieši pievienot GreenPAK uzlabotās attīstības platformai pie paplašināšanas savienotāja, kā parādīts 21. attēlā.

Kopā ar GreenPAK uzlabotās attīstības platformu ir ļoti vienkārši veikt signālu mērījumus ātrai pārbaudei. Piemēram, 22. attēlā parādīts signālu kopums (attiecīgi CLOCK, ADC INT izeja un DCMP OUT+ izeja), ko uztvēra HP 54620A loģiskais analizators. Viļņu formas aktivizē OUT+ signāla augošā mala (diapazonā, kas apzīmēts kā “A> B”), tāpēc šī ir viļņu formas uztveršana, kad starp analogo ieeju tiek konstatēts jauns maksimālais spriegums. Faktiski tas tika iegūts, pagriežot vienu no novērtēšanas padomes TrimPots, lai palielinātu atbilstošo spriegumu, kas parādīts 22. attēlā.

23. attēlā parādīta Vērtēšanas padomes shēma.

Secinājums

Šajā pamācībā mēs ieviesām astoņu kanālu maksimālā (vai min) sprieguma meklētāju, ko izmantot kā kopēju papildinājumu daudzkanālu vadības sistēmām. Piedāvātā pieeja izmanto GreenPAK komponentu uzlabotās funkcijas un parāda, kā ir iespējams integrēt vienā mikroshēmā analogās un digitālās funkcijas. Vairākas komerciālās IC var aizstāt ar Dialog GreenPAK, lai varētu samazināt lietojumprogrammas lielumu un izmaksas.

Ieteicams:

Sprieguma monitors augstsprieguma baterijām: 3 soļi (ar attēliem)

Sprieguma monitors augstsprieguma baterijām: šajā rokasgrāmatā es jums paskaidrošu, kā es izveidoju akumulatora sprieguma monitoru savam elektriskajam longboardam. Uzstādiet to, kā vēlaties, un pievienojiet akumulatoram tikai divus vadus (Gnd un Vcc). Šajā rokasgrāmatā tika pieņemts, ka akumulatora spriegums pārsniedz 30 voltus

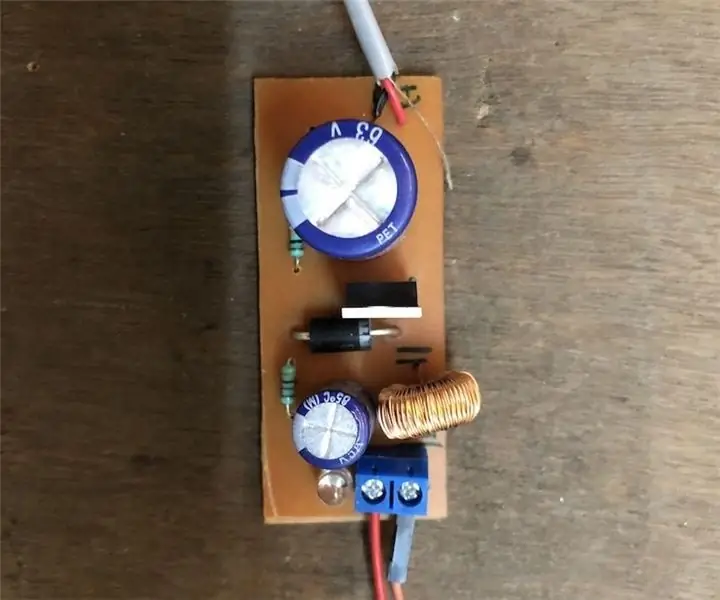

DC - līdzstrāvas sprieguma pazemināšanas slēdža režīms Buck sprieguma pārveidotājs (LM2576/LM2596): 4 soļi

DC-līdzstrāvas sprieguma pazemināšanas slēdža režīms Buck sprieguma pārveidotājs (LM2576/LM2596): ļoti efektīva buks pārveidotāja izgatavošana ir grūts darbs, un pat pieredzējušiem inženieriem ir vajadzīgi vairāki dizaini, lai tie nonāktu pie pareizā. ir līdzstrāvas līdzstrāvas pārveidotājs, kas samazina spriegumu (vienlaikus palielinot

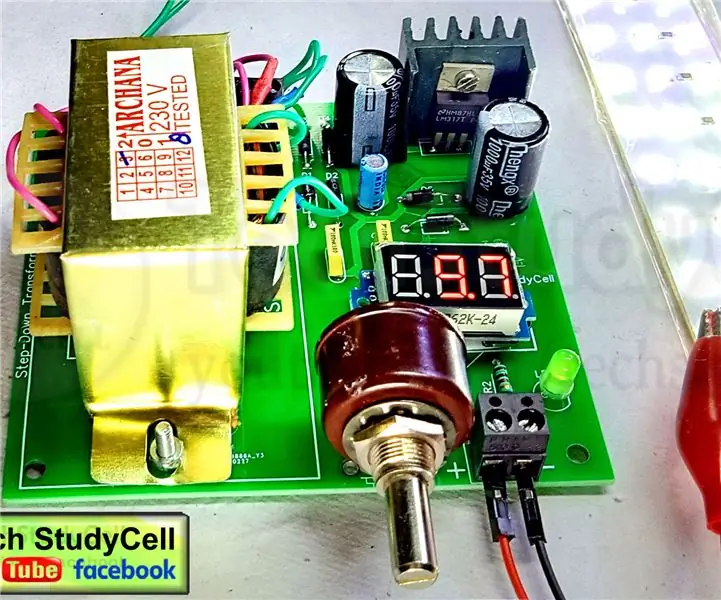

Regulējams sprieguma līdzstrāvas padeve, izmantojot sprieguma regulatoru LM317: 10 soļi

Regulējams sprieguma līdzstrāvas padeve, izmantojot LM317 sprieguma regulatoru: Šajā projektā esmu izstrādājis vienkāršu regulējama sprieguma līdzstrāvas barošanas avotu, izmantojot LM317 IC ar LM317 barošanas shēmas shēmu. Tā kā šai shēmai ir iebūvēts tilta taisngriezis, lai mēs varētu tieši savienot 220V/110V maiņstrāvas padevi pie ieejas

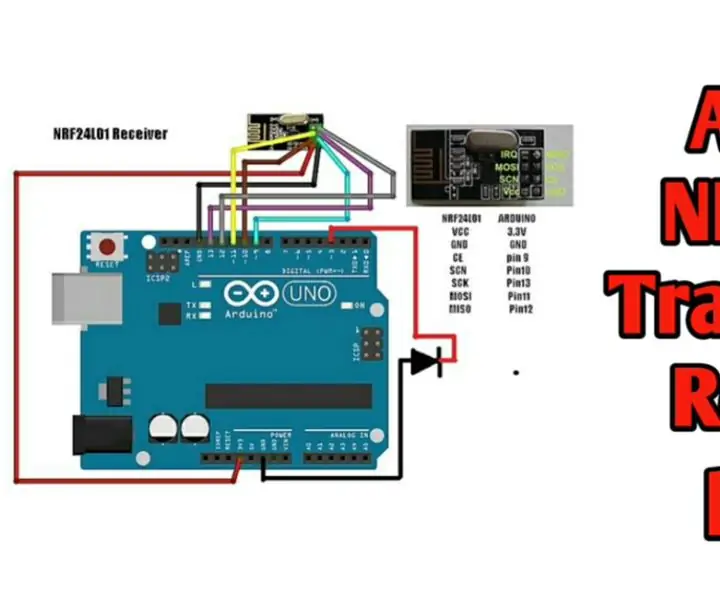

Bezvadu tālvadība, izmantojot 2,4 GHz NRF24L01 moduli ar Arduino - Nrf24l01 4 kanālu / 6 kanālu raidītāja uztvērējs kvadrakopteram - Rc helikopters - Rc lidmašīna, izmantojot Ardui

Bezvadu tālvadība, izmantojot 2,4 GHz NRF24L01 moduli ar Arduino | Nrf24l01 4 kanālu / 6 kanālu raidītāja uztvērējs kvadrakopteram | Rc helikopters | Rc lidmašīna, izmantojot Arduino: lai vadītu Rc automašīnu | Kvadkopters | Drons | RC plakne | RC laiva, mums vienmēr ir nepieciešams uztvērējs un raidītājs, pieņemsim, ka RC QUADCOPTER mums ir nepieciešams 6 kanālu raidītājs un uztvērējs, un šāda veida TX un RX ir pārāk dārgi, tāpēc mēs to izgatavosim savā

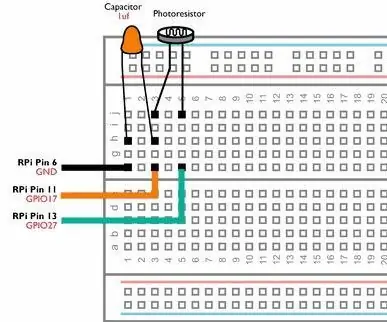

Raspberry Pi GPIO shēmas: LDR analoga sensora izmantošana bez ADC (analogā digitālā pārveidotāja): 4 soļi

Raspberry Pi GPIO shēmas: LDR analoga sensora izmantošana bez ADC (analogs digitālajam pārveidotājam): mūsu iepriekšējos norādījumos mēs parādījām, kā jūs varat saistīt Raspberry Pi GPIO tapas ar gaismas diodēm un slēdžiem un kā GPIO tapas var būt augstas vai Zems. Bet ko tad, ja vēlaties izmantot savu Raspberry Pi ar analogo sensoru? Ja mēs vēlamies izmantot