Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:57.

- Pēdējoreiz modificēts 2025-01-23 14:59.

Aparatūras loģisko shēmu projektēšana var būt jautra. Vecais skolas veids, kā to izdarīt, bija ar NAND vārtiem, uz maizes dēļa, savienotiem ar džemperu vadiem. Tas joprojām ir iespējams, taču nepaiet daudz laika, līdz vārtu skaits iziet no rokām. Jaunāka iespēja ir izmantot FPGA (Field Programmable Gate Array). Šīs mikroshēmas var pārvērsties par jebkuru digitālo loģisko shēmu, kuru varat izveidot, taču tās nav lētas un viegli pieejamas. Es parādīšu, kā šo FPGA var aizstāt ar lētu Atmega mikroshēmu no Arduino UNO, efektīvi ievietojot digitālo shēmu DIP paketē, kas ir ļoti draudzīga maizei.

1. darbība: izveidojiet ķēdi, kuru pārstāvēs "FPGA"

Es izveidošu 2 bitu + 2 bitu saskaitītāju. Tas aizņem divus pārus loģiskās ievades tapas un izvada vienu tripletu izejas tapas.

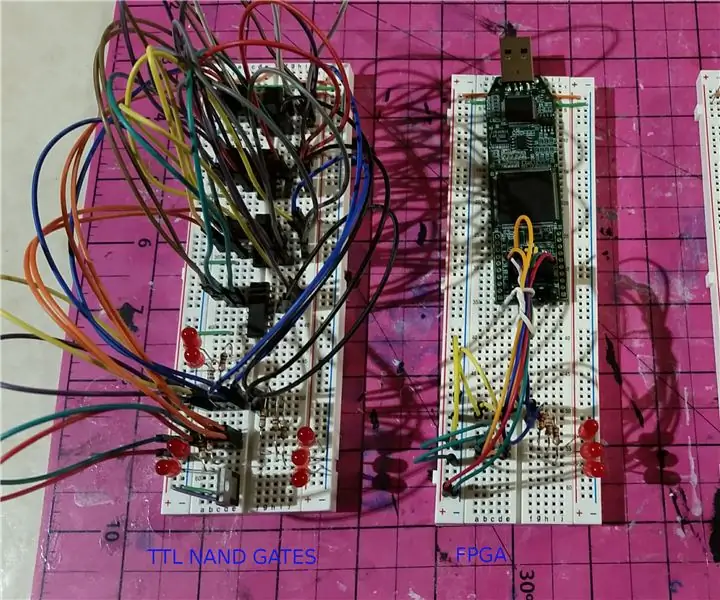

Lai to izdarītu ar NAND vārtiem, skatiet shēmu attēlā. Tam nepieciešami 14 NAND vārti. Es izmantoju četras četrkodolu NAND vārtu TTL mikroshēmas un pievienoju tās maizes dēļam.

Es pievienoju dažas gaismas diodes (neaizmirstiet strāvas ierobežošanas rezistorus), lai parādītu, kad ieejas un izejas tapas bija ieslēgtas (augstas) un kad tās bija izslēgtas (zemas). Lai virzītu ievades tapas, es tās vai nu pārlēku uz zemes sliedi, vai uz pozitīvās jaudas sliedi.

Šī shēma darbojas, taču tā jau aizņem 4 TTL mikroshēmas un ir žurku vadu ligzda. Ja būtu vajadzīgi vairāk gabaliņu, būtu vairāk maizes dēļu un vairāk džemperu. Ļoti ātri ķēdes izmērs izkļūtu no rokām.

Kā piezīmi, strādājot ar TTL vārtiem, tie neizraisa tieši 0V vai 5V, kā varētu gaidīt. Viņi bieži izvada ap 3V "augstam", bet precīzs spriegums ir ļoti plašā diapazonā. Tai pašai shēmai, kurā tiek izmantotas CMOS ekvivalentas mikroshēmas, būtu labāk tieši 0V līdz precīzi 5V svārstības.

2. darbība: ievadiet FPGA

FPGA ir fantastiska mikroshēma, kas burtiski var kļūt par jebkuru loģisko vārtu kombināciju, kas savienota jebkurā kombinācijā. Viens projektē "ķēdi" aparatūras dizaina valodā (HDL). Šādas valodas ir vairākas, no kurām vienu sauc par Verilog. Attēlā redzamais.v fails ir divu bitu saskaitītāja Verilog ekvivalents. Zemāk esošais.pch fails ir nepieciešams arī, lai verilog failā norādītās ievades un izvades tapas piešķirtu reālām mikroshēmas aparatūras tapām.

Šajā gadījumā es izmantoju Lattice Semiconductors iCEstick izstrādes paneli (https://www.latticesemi.com/icestick). Faktiskā FPGA mikroshēma ir iCE40HX-1k ar nedaudz vairāk nekā 1000 vārtiem, no kuriem katrs var kļūt par jebkuru loģisko vārtu. Tas nozīmē, ka visi vārti var būt NAND vārti vai VAI vārti, NAV vārti, NOR, XOR utt. Turklāt katrs vārts var apstrādāt vairāk nekā divas ievades. Tas ir raksturīgi katram ražotājam, bet iCE40s katrs vārts var apstrādāt 4 ieejas. Tādējādi katrs vārts ir daudz spējīgāks par 2 ieejas NAND vārtiem.

Man bija jāpiešķir 4 ieejas priedes un 3 izejas tapas fiziskajām tapām attiecīgi 91, 90, 88, 87, 81, 80 un 79. Tas ir raksturīgi fpga mikroshēmai un sadalīšanas plāksnei, kurā tā ir ieslēgta, un tam, kā šīs tapas ir savienotas ar PMOD portu. Tas ir pieejams šīs FPGA plates datu lapās.

Lattice nodrošina savu rīku ķēdi, lai sintezētu (FPGA ekvivalents CPU apkopošanai) shēmas no Verilog, bet es izmantoju bezmaksas atvērtā pirmkoda rīku ķēdes icestorm (https://www.clifford.at/icestorm/). Instalēšanas instrukcijas ir pieejamas šajā vietnē. Ja ir instalēta ledus vētra un verilog un pcf fails, komandas, lai ielādētu šo shēmu FPGA, ir šādas:

yosys -p "synth_ice40 -blif twoBitAdder.v" twoBitAdder.blif

arachne -pnr -d 1k -p iCEstick.pcf twoBitAdder.blif -o twoBitAdder.asc

ledus iepakojums twoBitAdder.asc twoBitAdder.bin

iceprog twoBitAdder.bin

Tas darbojas lieliski, taču, ieskaitot šīs iCEstick nosūtīšanu, būs jāmaksā aptuveni 30 USD. Tas nav lētākais digitālās shēmas veidošanas veids, taču tas ir spēcīgs. Tam ir vairāk nekā 1000 vārtu, un šai nelielajai ķēdei tas izmanto tikai 3 no tiem. NAND vārtu ekvivalentā tika izmantoti 14 vārti. Tas ir saistīts ar faktu, ka katrs vārts var kļūt par jebkura veida vārtiem, un katrs vārts faktiski ir 4 ieejas vārti. Katrs vārts var paveikt vairāk. Ja jums ir nepieciešams vairāk vārtu, iCEstick ir lielāks brālis ar 8000 vārtiem, kas maksā apmēram divas reizes. Citiem ražotājiem ir citi piedāvājumi, taču cena var kļūt diezgan augsta.

3. darbība: no FPGA uz Arduino

FPGA ir lieliski, taču tie var būt dārgi, grūti pieejami un nav ļoti draudzīgi maizei. Maizei draudzīga un lēta mikroshēma ir Atmega 328 P, kas tiek piegādāts glītā DIP iepakojumā, kas ir ideāli piemērots rīvdēļam. To var iegādāties arī par aptuveni 4 USD. Šī ir Arduino UNO sirds. Jūs, protams, varētu izmantot visu UNO, taču esiet lēti, mēs varam atvilkt Atmega 328 P no UNO un izmantot to atsevišķi. Tomēr es izmantoju UNO valdi kā Atmega programmētāju.

Šajā brīdī jums būs nepieciešams

1. Arduino UNO ar noņemamu Atmega 328P centrālo procesoru.

2. Vēl viens Atmega 328P ar iepriekš sadedzinātu Arduino sāknēšanas ielādētāju, lai aizstātu to, kuru mēs gatavojamies izņemt no ANO. (Pēc izvēles, pieņemot, ka joprojām vēlaties izmantot lietojamu UNO).

Mērķis ir pārvērst verilog failu par arduino projektu, ko var ielādēt 328P. Arduino pamatā ir C ++. Ērti ir tulkotājs no Verilog uz C ++, ko sauc par Verilator (https://www.veripool.org/wiki/verilator). Verilatoru ir paredzēts izmantot aparatūras dizaineriem, kuriem pirms modeļu piesaistīšanas dārgai aparatūrai ir nepieciešams simulēt savus dizainus. Verilatoru krusts apkopo verogogu uz C ++, pēc tam lietotājs nodrošina pārbaudes jostu, lai nodrošinātu simulētus ievades signālus un ierakstītu izejas signālus. Mēs to izmantosim, lai saspiestu verilogu dizainu Atmega 328P, izmantojot Arduino instrumentu ķēdi.

Vispirms instalējiet Verilator. Izpildiet norādījumus vietnē

Instalējiet arī Arduino IDE un pārbaudiet, vai tas var izveidot savienojumu ar Arduino UNO, izmantojot USB.

Mēs izmantosim to pašu verilog failu kā FPGA, izņemot to, ka tapu nosaukumi ir jāmaina. Katra sākumam pievienoju pasvītrojumu (_). Tas ir nepieciešams, jo arduino bibliotēkās ir iekļauts galvenes fails, kas tādas lietas kā B0, B001 utt. Tulko binārajos skaitļos. Citi ievades tapu nosaukumi būtu labi, kādi tie ir, bet B0 un B1 būtu izraisījuši būves kļūmi.

Katalogā, kurā ir twoBitAdder.v un iCEstick.pcf, palaidiet šo:

verilators -Siena --cc twoBitAdder.v

Tādējādi tiks izveidots apakšdirektorijs ar nosaukumu obj_dir, kurā būs vairāki jauni faili. Mums ir nepieciešami tikai galvenes un cpp faili VtwoBitAdder.h, VtwoBitAdder.cpp, VtwoBitAdder_Syms.h un VtwoBitAdder_Syms.cpp.

Arduino IDE izveidojiet jaunu skici ar nosaukumu twoBitAdder.ino. Tas izveidos ino failu jaunā direktorijā, ko sauc arī par twoBitAdder, jūsu Arduino skiču grāmatas direktorijā. Kopējiet savus failus VtwoBitAdder.h un VtwoBitAdder.cpp šajā mapē twoBitAdder savā Arduino mapē.

Tagad nokopējiet galvenes failus no verilatora instalācijas.

cp/usr/local/share/verilator/include/verilated*.

beidzot nokopējiet std c ++ bibliotēkā vietnē https://github.com/maniacbug/StandardCplusplus. Saskaņā ar viņu instalēšanas instrukcijām "Šī ir instalēta tāpat kā parasta Arduino bibliotēka. Izpakojiet izplatīšanas saturu mapē" bibliotēkas "zem jūsu skiču grāmatas. Piemēram, mana skiču grāmata atrodas vietnē/home/maniacbug/Source/Arduino, tāpēc šī bibliotēka atrodas mapē/home/maniacbug/Source/Arduino/libraries/StandardCplusplus.

Pēc Arduino IDE instalēšanas noteikti atiestatiet to."

Tagad nomainiet vietnes twoBitAdder.ino saturu ar tajā norādīto. Šī ir pārbaudes siksna, ko sagaida verilators, kas izveido ievades/izvades tapas, pēc tam cilpā, nolasa ievades tapas, padod tās VtwoBitAdder (mūsu ķēdes tulkotā versija), pēc tam nolasa VtwoBitAdder izejas un piemēro tos pie izejas tapām.

Šo programmu vajadzētu apkopot un izpildīt Arduino UNO.

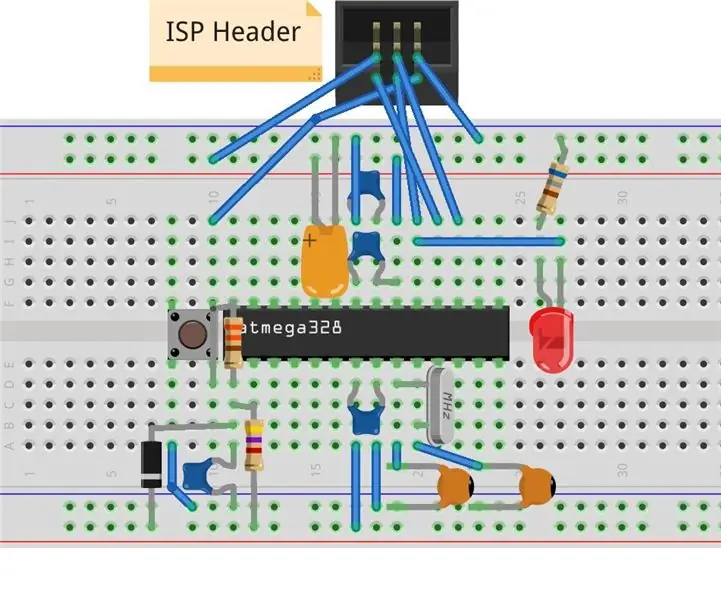

4. solis: no Arduino līdz DIP mikroshēmai uz maizes dēļa

Tagad, kad programma darbojas Arduino, mums vairs nav nepieciešama pati Arduino tāfele. Viss, kas mums nepieciešams, ir CPU.

Uzmanīgi noņemiet Atmega 328P no ligzdas Arduino UNO un pēc izvēles ievietojiet tā nomaiņu.

Uzlieciet Atmega 328P uz maizes dēļa. Ielieciet galu ar maizi uz augšu uz maizes dēļa. 1. tapa ir augšējā kreisā tapa. 2. tapa ir nākamā uz leju un tā tālāk līdz 14. tapai, kas atrodas apakšējā kreisajā stūrī. Tad tapa 15 ir labajā apakšējā stūrī, un tapas no 16 līdz 28 tiek skaitītas atpakaļ mikroshēmas labajā pusē.

Savienojiet tapas 8 un 22 ar zemi.

Pievienojiet 7. tapu VCC (+5 V).

Pievienojiet 16Mhz kvarca kristālu starp tapām 9 un 10. Arī nelielu kondensatoru (22pF) starp tapu 9 un zemi, kā arī starp tapu 10 un zemi. Tas dod Atmega 328P 16Mhz pulksteņa ātrumu. Citur ir norādījumi par 328P mācīšanu tā vietā izmantot savu iekšējo 8Mhz pulksteni, kas ietaupītu pāris daļas, taču tas palēninātu procesoru.

Arduino GPIO porti 5, 6, 7 un 8, kurus mēs izmantojām ievades tapām, patiesībā ir Atmega 328P fiziskās tapas 11, 12, 13, 14. Tās būtu četras apakšējās tapas kreisajā pusē.

Arduino GPIO pieslēgvietas 11, 10 un 9, kuras mēs izmantojām izejas tapām, patiesībā ir Atmega 328P fiziskās tapas 17, 16, 15. Tas būtu trīs apakšējās tapas labajā pusē.

Es pievienoju gaismas diodes šīm tapām, kā iepriekš.

5. darbība. Secinājums

TTL mikroshēmas darbojas, taču, lai kaut ko izveidotu, ir nepieciešams daudz no tiem. FPGA darbojas patiešām labi, bet nav lēti. Ja jūs varat dzīvot ar mazākām IO tapām un zemāku ātrumu, tad Atmega 328P var būt jūsu mikroshēma.

Dažas lietas, kas jāpatur prātā:

FPGA:

Pro

- Var apstrādāt ātrgaitas signālus. Tā kā nav CPU, kas kavētu apstrādi līdz vienai instrukcijai vienlaikus, ierobežojošais faktors ir izplatīšanās aizkavēšanās caur dotajā ķēdē esošajiem vārtiem. Daudzos gadījumos tas var būt daudz ātrāk nekā mikroshēmā iekļautais pulkstenis. Manam projektam aprēķinātā kavēšanās būtu ļāvusi twoBitAdder reaģēt uz aptuveni 100 miljoniem ievades vērtību izmaiņu sekundē (100Mhz), lai gan borta pulkstenis ir tikai 12 MHz kristāls.

- Tā kā dizains kļūst sarežģītāks, esošo ķēžu veiktspēja nepasliktinās (daudz). Tā kā ķēžu pievienošana audumam vienkārši liek kaut ko jaunu neizmantotā nekustamajā īpašumā, tas neietekmē esošās shēmas.

- Atkarībā no FPGA pieejamo IO tapu skaits var būt ļoti liels, un tie parasti nav paredzēti kādam konkrētam mērķim.

Con

- Var būt dārgi un/vai grūti sasniedzami.

- Parasti tiek piegādāts BGA iepakojumā, kuram jebkurā amatieru projektā nepieciešama mikroshēma, lai strādātu ar mikroshēmu. Ja jūs to veidojat dizainā ar pielāgotu daudzslāņu SMT PCB, tā nav problēma.

- Lielākā daļa FPGA ražotāju nodrošina savu slēgtā pirmkoda projektēšanas programmatūru, kas dažos gadījumos var maksāt naudu vai kuriem ir licences derīguma termiņš.

Arduino kā FPGA:

Pro

- Lēti un viegli iegūstami. Vienkārši meklējiet atmega328p-pu vietnē Amazon. Viņiem vajadzētu būt apmēram USD 4 par gabalu. Vairāki pārdevēji tos pārdod 3 vai 4 partijās.

- Šī ir DIP pakete, kas lieliski iekļaujas maizes plāksnē ar ārējām tapām.

- Šī ir 5 V ierīce, kas var atvieglot saskarni ar citām 5 V ierīcēm.

Con

- ATMEGA328P ir ierobežots skaits IO tapu (23), un vairākas no tām ir rezervētas īpašiem uzdevumiem.

- Palielinoties ķēdes sarežģītībai, palielinās Arduino cilpas metodē izpildītā koda daudzums, kas nozīmē, ka katra cikla ilgums ir garāks.

- Pat ja ķēdes sarežģītība ir zema, katram ciklam ir vajadzīgas daudzas CPU instrukcijas, lai ielādētu ievades tapu vērtības un ierakstītu izejas tapas vērtības un atgrieztos cilpas augšdaļā. Izmantojot 16Mhz kristālu, pat ar vienu instrukciju pulksteņa ciklā cilpa nedarbosies vairāk kā varbūt 1 miljonu reižu sekundē (1Mhz). Tomēr lielākajai daļai amatieru elektronikas projektu tas ir daudz ātrāk nekā nepieciešams.

Ieteicams:

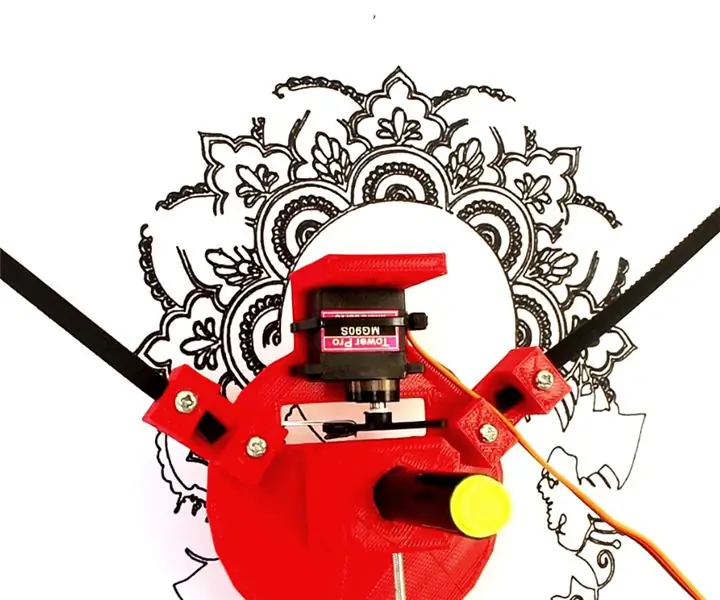

MXY dēlis - zema budžeta XY ploteru zīmēšanas robotu dēlis: 8 soļi (ar attēliem)

MXY dēlis - zema budžeta XY ploteru zīmēšanas robotu dēlis: Mans mērķis bija izveidot mXY tāfeli tā, lai XY ploteru zīmēšanas mašīna būtu ar mazu budžetu. Tāpēc es izveidoju tāfeli, kas atvieglo tiem, kas vēlas izveidot šo projektu. Iepriekšējā projektā, izmantojot 2 gab. Nema17 soļu motorus, šī tāfele

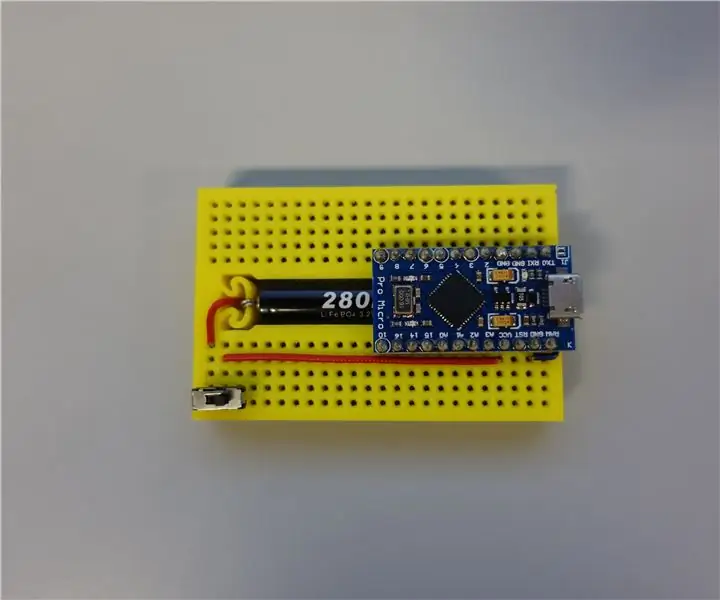

Dev Board maizes dēlis: 12 soļi (ar attēliem)

Izstrādātāja dēļa maizes dēlis: šajā pamācībā ir parādīts, kā izveidot speciāli pielāgotu maizes dēli izstrādātāja dēlim

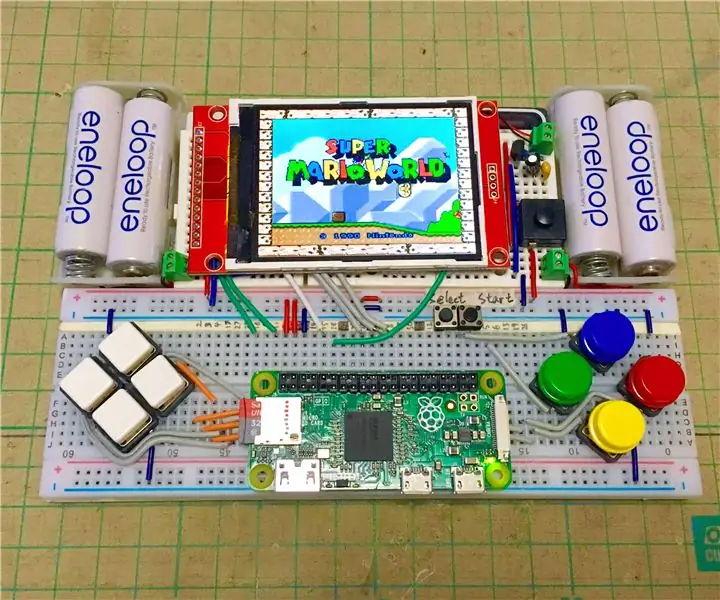

Maizes dēlis RetroPie: 33 soļi (ar attēliem)

Breadboard RetroPie: Šī instrukcija parāda, kā izveidot Breadboard RetroPie, bez lodēšanas, bez 3D printera, nav nepieciešams lāzera griezējs. Spēļu automāta izveide ir ļoti labs projekts, lai sākotnēji mācītos elektroniku. Tomēr lielāko daļu RetroPie projektu, ko būvējuši pieaugušie

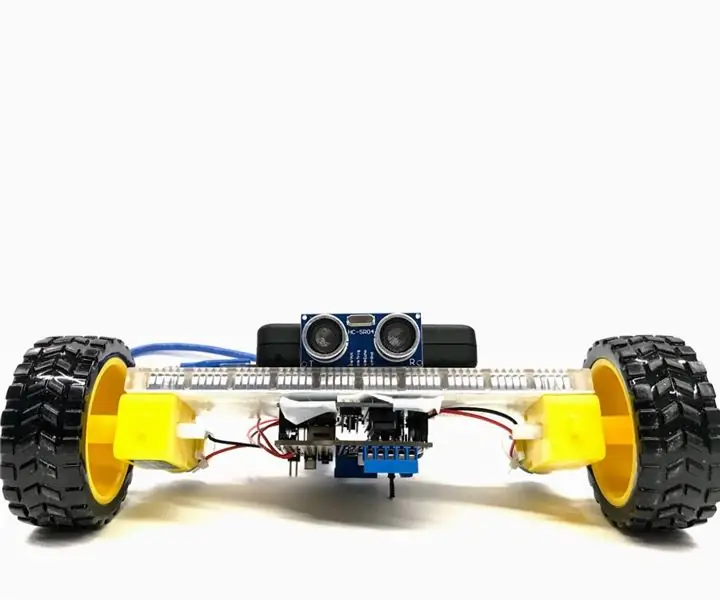

TfCD - pašbraucošs maizes dēlis: 6 soļi (ar attēliem)

TfCD-pašbraucošs maizes dēlis: šajā pamācībā mēs demonstrēsim vienu no tehnoloģijām, kas bieži tiek izmantota autonomajos transportlīdzekļos: ultraskaņas šķēršļu noteikšana. Pašpiedziņas automašīnās šī tehnoloģija tiek izmantota šķēršļu atpazīšanai nelielā attālumā (< 4 m), f

Maizes dēlis Arduino pareizajā veidā: 5 soļi (ar attēliem)

Maizes dēlis Arduino pareizais ceļš: tur burtiski ir simtiem maizes dēļu Arduinos, tad kas šajā ir atšķirīgs? Ir vairākas lietas, kuras vairumam un pat pašam Arduino nedarbojas pareizi. Pirmkārt, analogā piegāde ir saistīta ar