Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:53.

- Pēdējoreiz modificēts 2025-01-23 14:59.

Savienojiet savu Mojo izstrādes paneli ar ārējām ieejām, izmantojot šo vairogu.

Kas ir Mojo attīstības padome?

Mojo attīstības padome ir izstrādes padome, kuras pamatā ir Xilinx spartan 3 FPGA. Dēlis ir izgatavots Alchitry. FPGA ir ļoti noderīgi, ja vienlaikus ir jāizpilda vairāki procesi.

Kas jums būs vajadzīgs?

Piegādes

Mojo attīstības padome

Gerbera fails

8 x 15k omi rezistori (pēc izvēles*)

4 x 470 omi rezistori

4 x 560 omi rezistori

4 x CC septiņu segmentu displeji

4 x 3 mm gaismas diodes

4 x SPDT taustes slēdži

1 x 4 pozīciju virsmas stiprinājuma DIP slēdzis

2 x 25 x 2 vai 4 x 25 galvenes

1x 2 x 5 kontaktu kārbas galva

Lodāmurs

Lodēt

Plūsma

*(ja šie rezistori netiek izlaisti, attiecīgajām tapām ir jāiespējo iekšējā vilkšana/nolaišana)

1. darbība: augšupielādējiet Gerber jūsu izvēlētajam datoru ražotājam

Saviem dēļiem es pasūtīju no JLC PCB.

Vienīgās izmaiņas, ko es izdarīju, bija krāsa, kurai vēlējos pieskaņoties Mojo melnajam.

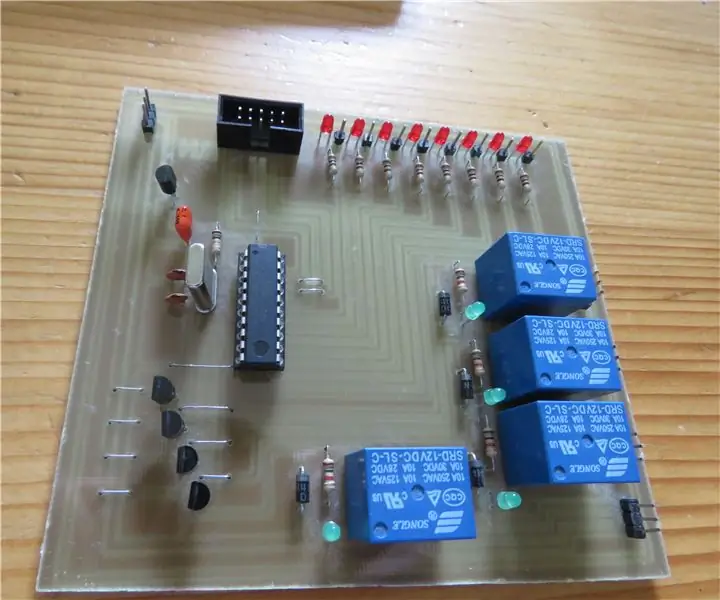

2. solis: valdes montāža

Lodējot, es vienmēr uzskatu, ka ir lietderīgi vispirms pielodēt zemākās daļas, tāpēc, sākot ar rezistoriem, ir laba ideja.

R5, R6, R7, R8, R9, R10, R11 un R12 ir 15 k omi rezistori, ko izmanto slēdžu nolaišanai (ja izmantojat iekšējo pievilkšanu/nolaišanu, ignorējiet to).

R1, R2, R3, R4 ir 560 omu rezistori, kas ir atbildīgi par strāvas ierobežošanu caur 7 segmentu displeju.

R13, R14, R15, R16 ir 470 omu rezistori, kas ir atbildīgi par strāvas ierobežošanu caur 4 gaismas diodēm.

Tālāk lodējiet iegremdēšanas slēdzi, taustes slēdžus, gaismas diodes, septiņu segmentu displejus un kastes galvenes savienotāju šādā secībā.

Tagad ievietojiet 25 x 2 (vai 2 25 x 1) mojo, lai izlīdzinātu tapas. Izlīdziniet vairogu ar tapām un pielodējiet to vietā.

3. darbība: programmatūras iestatīšana

Programmatūrai, kas atsaucas uz vietni Alchitry, jūs informēsit, kas jums nepieciešams, lai sāktu darbu un instalētu Xilinx ISE. Tomēr mainot.ucf failu, lai tas zinātu, kuras tapas ir savienotas ar to, kas ir svarīgi, lai jūsu programma darbotos.

Šeit ir.ucf fails, ko izmantoju kopā ar vairogu:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARTS = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARTS = LVTTL; NET "cclk" LOC = P70 | IOSTANDARTS = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARTS = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARTS = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARTS = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARTS = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARTS = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARTS = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARTS = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARTS = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARTS = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARTS = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARTS = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARTS = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARTS = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARTS = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARTS = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARTS = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARTS = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARTS = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARTS = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARTS = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARTS = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARTS = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARTS = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARTS = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARTS = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARTS = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARTS = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARTS = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARTS = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARTS = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARTS = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARTS = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARTS = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARTS = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARTS = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARTS = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARTS = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARTS = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARTS = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARTS = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARTS = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARTS = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARTS = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARTS = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARTS = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARTS = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARTS = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARTS = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARTS = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARTS = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARTS = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARTS = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARTS = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARTS = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARTS = LVTTL;

Atcerieties, ja neesat instalējis nolaižamos rezistorus, lai rediģētu.ucf tapas ar

| VILKT LEJĀ; o

| UZVILKT;

Ja vēlaties izmantot bloku jebkam citam, savienojumi ir šādi. Kreisais ir bloka tapas numurs, bet labais ir mojo tapas numurs, kas jums jāpiešķir savā.ucf failā:

tapa 1 = 29

2. tapa = 51

tapa 3 = 32

pin 4 = 41

tapa 5 = 34

pin 6 = 35

tapa 7 = 40

8. tapa = 33

pin 9 = GND

tapa 10 = +V

Ieteicams:

DIY ESP32 attīstības padome - ESPer: 5 soļi (ar attēliem)

DIY ESP32 attīstības padome - ESPer: Tik nesen es lasīju par daudziem IoT (lietu internets) un ticiet man, es vienkārši nevarēju gaidīt, lai pārbaudītu kādu no šīm brīnišķīgajām ierīcēm ar iespēju izveidot savienojumu ar internetu, sevi un ķeras pie darba. Par laimi iespēja

Izveidojiet savu attīstības padomi, izmantojot mikrokontrolleru: 3 soļi (ar attēliem)

Izveidojiet savu attīstības padomi, izmantojot mikrokontrolleri: Vai jūs kādreiz vēlējāties izveidot savu izstrādes paneli ar mikrokontrolleri, un jūs nezinājāt, kā. Šajā pamācībā es jums parādīšu, kā to izveidot. Viss, kas jums nepieciešams, ir zināšanas elektronikā, shēmu projektēšana un programmēšana. Ja jums ir kādi uzdevumi

JALPIC One attīstības padome: 5 soļi (ar attēliem)

JALPIC One attīstības padome: Ja sekojat maniem Instructables projektiem, jūs zināt, ka esmu liels JAL programmēšanas valodas cienītājs kombinācijā ar PIC mikrokontrolleri. JAL ir Pascal līdzīga programmēšanas valoda, kas izstrādāta Microchip 8 bitu PIC mikrokontrolleriem. Mo

Mikrokontrolleru izstrādes padomes izstrāde: 14 soļi (ar attēliem)

Mikrokontrolleru izstrādes padomes izveide: Vai esat veidotājs, hobijs vai hakeris, kurš vēlas pāriet no perfboard projektiem, DIP IC un mājās gatavotiem PCB uz daudzslāņu PCB, kas izgatavoti no dēļu mājām un SMD iepakojuma, kas ir gatavs masveida ražošanai? Tad šī pamācība ir paredzēta jums! Šis gui

AVR attīstības padome: 3 soļi

AVR attīstības padome: internets ir pilns ar projektiem ar Arduino. Kādu laiku visos Arduino datos trūkst informācijas par ATMEGA328 mikrokontrolleri. Šis inspicējamais vēlas atgūt sākumu, kā attīstīt projektus, izmantojot AVR mikrokontūru