Satura rādītājs:

- 1. darbība: kas ir Vivado HLS?

- 2. darbība: HLS video bibliotēka

- 3. solis: sintezēšana

- 4. darbība. Versija un cita informācija eksportēšanai

- 5. darbība. Eksportēšana uz Vivado IP bibliotēku

- 6. darbība: sintēze un eksporta analīze

- 7. darbība: IP bibliotēkas pievienošana Vivado

- 8. darbība. Jaunināšana

- 9. darbība. Papildu informācija un informācija

- 10. darbība: izvade un ievade

- 11. darbība. AXI reģistra saskarne

- 12. solis: datu plūsmas pragma

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:57.

- Pēdējoreiz modificēts 2025-01-23 14:59.

Vai esat kādreiz vēlējies video apstrādi reāllaikā, nepievienojot lielu latentumu vai iegultā sistēmā? Lai to izdarītu, dažreiz tiek izmantoti FPGA (lauka programmējamie vārtu masīvi); tomēr video apstrādes algoritmu rakstīšana aparatūras specifikācijas valodās, piemēram, VHDL vai Verilog, labākajā gadījumā ir nomākta. Ievadiet Xivadx rīku Vivado HLS, kas ļauj programmēt C ++ vidē un no tā ģenerēt aparatūras specifikācijas valodas kodu.

Nepieciešamās programmatūras:

- Vivado HLS

- Vivado

- (Ja izmantojat AXI reģistrus) Vivado SDK

(Pēc izvēles) Lejupielādējiet Xilinx veidotos piemērus šeit:

Xilinx HLS video piemēri

1. darbība: kas ir Vivado HLS?

Vivado HLS ir rīks, ko izmanto, lai pārvērstu c ++ līdzīgu kodu aparatūras struktūrās, kuras var ieviest FPGA. Tas ietver IDE šīs izstrādes veikšanai. Kad esat pabeidzis HLS koda izstrādi, varat eksportēt ģenerēto IP formātā lietošanai kopā ar Vivado.

Lejupielādējiet pievienotos failus un novietojiet tos netālu no vietas, kur veidosit savu projektu. (pārdēvējiet tos atpakaļ uz "top.cpp" un "top.h", ja tiem ir randomizēts nosaukums)

2. darbība: HLS video bibliotēka

Šajā rakstā HLS video bibliotēkai ir dokumentācija ar atsauces dizainu: XAPP1167Vēl viens labs resurss ir Xilinx Wiki lapa par to.

Sāciet Vivado HLS.

Izveidojiet jaunu projektu.

Paņemiet iepriekšējā solī lejupielādētos failus un pievienojiet tos kā avota failus. (Piezīme: faili netiek kopēti projektā, bet paliek vietā, kur tie ir)

Pēc tam izmantojiet pogu Pārlūkot, lai atlasītu augšējo funkciju.

Nākamajā lapā atlasiet izmantoto Xilinx daļu.

3. solis: sintezēšana

Risinājums => Palaist C sintēzi => Aktīvais risinājums

Pēc ~ 227,218 sekundēm tas būtu jādara. (Piezīme: jūsu faktiskais sintēzes laiks būs atkarīgs no daudziem faktoriem)

4. darbība. Versija un cita informācija eksportēšanai

Versiju numuri mijiedarbojas ar Vivado, lai jūs varētu atjaunināt IP dizainu. Ja tā ir neliela versijas maiņa, to var izdarīt vietā, kamēr galvenās versijas izmaiņas prasa manuāli pievienot jauno bloku un noņemt veco. Ja jūsu saskarnes nav mainījušās un versijas atjauninājums ir mazsvarīgs, atjauninājumu var darīts pilnīgi automātiski, nospiežot atjaunināšanas IP pogu. Vivado tcl konsolē varat palaist "report_ip_status", lai redzētu sava IP statusu.

Iestatiet versijas numurus un citu informāciju sadaļā Solution => Solution Settings…

Alternatīvi, šos iestatījumus var iestatīt eksportēšanas laikā.

5. darbība. Eksportēšana uz Vivado IP bibliotēku

Risinājums => Eksportēt RTL

Ja iepriekšējā darbībā neesat iestatījis IP bibliotēkas informāciju, varat to izdarīt tagad.

6. darbība: sintēze un eksporta analīze

Šajā ekrānā mēs varam redzēt statistiku par mūsu eksportēto moduli, kas parāda, ka tas atbilst mūsu pulksteņa periodam 10ns (100MHz) un cik daudz katra resursa tas izmanto.

Izmantojot šo kombināciju, mūsu kopsavilkuma pārskatu un mūsu datu plūsmas analīzi, mēs redzam, ka ir nepieciešami 317338 pulksteņa cikli * 10ns pulksteņa periods * 14 cauruļvada posmi = 0,04442732 sekundes. Tas nozīmē, ka kopējais latentums, ko pievieno mūsu attēlu apstrāde, ir mazāks par vienu divdesmitdaļu sekundes (ja tiek sasniegts 100 MHz frekvence).

7. darbība: IP bibliotēkas pievienošana Vivado

Lai izmantotu sintezēto IP bloku, tas būs jāpievieno Vivado.

Programmā Vivado pievienojiet savam projektam IP krātuvi, dodoties uz IP katalogu un ar peles labo pogu noklikšķinot uz "Pievienot repozitoriju …"

Dodieties uz savu Vivado HLS projektu direktoriju un atlasiet risinājumu direktoriju.

Tai jāziņo par atrasto IP.

8. darbība. Jaunināšana

Dažreiz jums ir jāveic izmaiņas savā HLS blokā pēc tā iekļaušanas Vivado dizainā.

Lai to izdarītu, varat veikt izmaiņas un atkārtoti sintezēt un eksportēt IP ar augstāku versijas numuru (sīkāku informāciju skatiet iepriekšējā solī par galvenajām/mazajām versijas numuru izmaiņām).

Pēc jaunās versijas eksportēšanas mainīšanas atsvaidziniet savas IP krātuves Vivado. To var izdarīt vai nu tad, kad Vivado pamana, ka IP krātuvē ir mainījies, vai arī to var aktivizēt manuāli. (Ņemiet vērā: ja atsvaidzināt IP krātuves pēc sākuma, bet pirms eksportēšanas pabeigšanas HLS, IP īslaicīgi nebūs, pagaidiet, līdz tas beidzas, un atsvaidziniet vēlreiz.)

Šajā brīdī vajadzētu parādīties logs ar informāciju, ka diskā ir mainīts IP, un tas dod iespēju to atjaunināt ar pogu "Jaunināt atlasīto". Ja izmaiņas bija nelielas versijas izmaiņas un neviena no saskarnēm nav mainīta, pēc tam nospiežot šo pogu, vecais IP tiks automātiski aizstāts ar jauno, pretējā gadījumā var būt nepieciešams vairāk darba.

9. darbība. Papildu informācija un informācija

Tālāk norādītās darbības sniedz vairāk informācijas par to, kā darbojas HLS sintēze un ko ar to var darīt.

Projekta piemēru, kurā tiek izmantots HLS sintezēts IP bloks, skatiet šajā pamācībā.

10. darbība: izvade un ievade

Izejas un ieejas galīgajā IP blokā tiek noteiktas, analizējot sintezatoru datu plūsmu augšējā funkcijā un ārpus tās.

Līdzīgi kā VHDL vai verilog, HLS ļauj norādīt informāciju par savienojumiem starp IP. Šīs rindas ir piemēri tam:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE ass ports = video_in saišķis = INPUT_STREAM #pragma HLS INTERFACE ass ports = video_out saišķis = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite ports = x saišķis = CONTROL_BUS nobīde = 0x14 #pragma h_xbite

Jūs varat redzēt, kā šīs direktīvas ietekmē IP blokā izstādītos portus.

11. darbība. AXI reģistra saskarne

Lai ievadītu/izvadītu uz/no IP bloka uz PS, labs veids, kā to izdarīt, ir AXI saskarne.

To varat norādīt savā HLS kodā, ieskaitot nobīdes, kas jāizmanto, lai vēlāk piekļūtu vērtībai šādi:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite ports = x saišķis = CONTROL_BUS nobīde = 0x14

#pragma HLS INTERFACE s_axilite ports = y saišķis = CONTROL_BUS nobīde = 0x1C #pragma HLS datu plūsma

x = 42;

y = 0xDEADBEEF; }

Kad Vivado ir pareizi pievienots, varat piekļūt vērtībām, izmantojot šo kodu Vivado SDK:

#include "parametri.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Tādējādi jums būs 42 x un 0xdeadbeef y

12. solis: datu plūsmas pragma

#Pragma DATAFLOW iekšpusē koda ieviešanas veids mainās no parastās C ++. Kods tiek konstruēts tā, lai visas instrukcijas vienmēr darbotos dažādās datu daļās (domājiet par to kā par montāžas līniju rūpnīcā, katra stacija nepārtraukti strādā, veicot vienu funkciju un nododot to nākamajai stacijai)

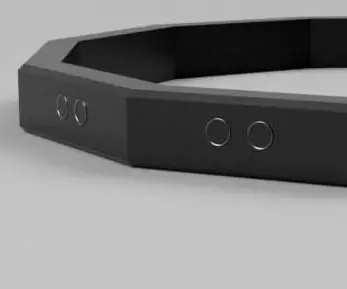

no attēla var redzēt, ka katra no direktīvām

Lai gan šķiet, ka tie ir normāli mainīgie, img objekti faktiski tiek ieviesti kā mazi buferi starp komandām. Ja attēlu izmanto kā funkcijas ievadi, tas tiek “patērēts” un vairs nav izmantojams. (Tāpēc ir vajadzīgas komandu dublikāti)

Ieteicams:

Mana pirmā sintēze: 29 soļi (ar attēliem)

Mana pirmā sintezācija: Bērnu sintezators radās, kad es sēdēju sačokurojusies pār sajukušu sintezatora vadu jucekli. Mans draugs Olivers pienāca klāt, novērtēja situāciju un teica: "Jūs zināt, ka jums ir izdevies izgatavot pasaulē sarežģītāko bērnu rotaļlietu." Kamēr mans sākotnējais r

Fonohronoksils - 360 grādu sintēze: 3 soļi (ar attēliem)

Phono -Chronoxyle - 360 grādu sintēze: Džūljena Signoleta tēlniece no Parīzes un mūziķis Matiass Durands vērsās pie manis, lai izveidotu interaktīvu skaņas instalāciju Parc Floral Parīzē Nuit Blanche 2019. Instalācija būtu ārpus durvīm, un es nebūtu klāt tās laikā iekšā

Retro runas sintēze. Daļa: 12 IoT, mājas automatizācija: 12 soļi (ar attēliem)

Retro runas sintēze. Daļa: 12 IoT, mājas automatizācija: Šis raksts ir 12. sērija par mājas automatizācijas instrukcijām, kas dokumentē, kā izveidot un integrēt IoT Retro runas sintēzes ierīci esošā mājas automatizācijas sistēmā, ieskaitot visas nepieciešamās programmatūras funkcijas, lai varētu

Analogās skaņas sintēze datorā: 10 soļi (ar attēliem)

Analogās skaņas sintēze datorā: patīk šo veco analogo sintezatoru skaņa? Vai vēlaties spēlēt ar vienu savā laikā, savā vietā, cik ilgi vien vēlaties, BEZ MAKSAS? Šeit piepildās jūsu mežonīgākie Moog sapņi. Jūs varat kļūt par elektronisko ierakstu mākslinieku vai

Modulārais " Flunk " Sintēze: 6 soļi

Modulārais " Flunk " Sintē: Modulārais Flunk sintezators ir Atari panku konsole ar papildu atloku iespējām. Tas rada impulsa vilni, izmantojot taimeri LM556. Atloku var izmantot citu signālu, piemēram, ģitāras, apstrādei, izmantojot atloka ieeju. To darbina divas 9 V baterijas. Viens