Satura rādītājs:

- 1. darbība. Digitālā sekvences lietotāja darbība

- 2. darbība. Tehniskā informācija

- 3. darbība: tehniskā informācija

- 4. solis: 7 segmentu pulksteņu dalītājs

- 5. solis: sitieni minūtē pulksteņa dalītājs

- 6. solis: pulksteņa dalītājs

- 7. darbība: atskaņot/apturēt/atlasīt štata mašīnu

- 8. darbība: atskaņot/apturēt/atlasīt štata mašīnu

- 9. darbība: izvadiet FSM

- 10. darbība: izvadiet FSM

- 11. darbība. Piezīme Piešķirt

- 12. darbība: izvades izvēle

- 13. solis: Square Wave Gen

- 14. darbība: 7 segmentu displejs

- 15. solis: galīgā izvēle

- 16. darbība. Ārējās ierīces: DAC

- 17. darbība. Ārējās ierīces: skaļrunis

- 18. darbība. Video demonstrācija

- 19. darbība: VHDL kods

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:58.

- Pēdējoreiz modificēts 2025-01-23 14:59.

CPE 133, Cal Poly San Luis Obispo

Projekta veidotāji: Jayson Johnston un Bjorn Nelson

Mūsdienu mūzikas industrijā viens no visbiežāk izmantotajiem “instrumentiem” ir digitālais sintezators. Katrs mūzikas žanrs, sākot no hiphopa līdz popmūzikai un pat kantrim, studijā izmanto digitālo sintezatoru, lai radītu sitienus un skaņas, kas vajadzīgas, lai iedzīvinātu viņu mūziku. Šajā apmācībā mēs izveidosim ļoti vienkāršu sintezatoru ar Basys 3 FPGA plati.

Sintezators varēs atskaņot četras izvēlētās ceturtdaļas notis ar nemainīgu sitienu skaitu minūtē. Lietotāji izmantos slēdžus, lai katru ceturkšņa noti piešķirtu mūzikas skaņai. Šim projektam mēs izmantojam 4 bitu digitālo analogo pārveidotāju (DAC), lai uztvertu plāksnes izvadi un pārvērstu to par analogo signālu. Pēc tam DAC izvade tiks ievadīta standarta datora skaļrunī, radot mūsu mūziku. Iespējami sešpadsmit diskrēti laukumi. Mēs ierobežosim savu sintezatoru līdz vienai oktāvai ar 12 notīm, kas atrodas starp vidējo C (261,6 Hz) un B4 (493,9 Hz). Lietotājam būs arī iespēja vienlaikus piešķirt vairākas piezīmes, kā arī piešķirt atpūtu, noklikšķinot uz piešķirt, kamēr neviens no augstuma slēdžiem nav pārvietots uz augšu. Kad katra piezīme ir izvēlēta un tiek atskaņota, burtu piezīme tiek parādīta 7 segmentu displejā. Mēs izmantosim arī trīs pogas uz tāfeles, vienu mūzikas atskaņošanai un apturēšanai, vienu sintezatora atiestatīšanai un “atlases” režīmā, bet trešo, lai katrai notij piešķirtu piķi atlases režīmā.

Kad lietotājs ir apmierināts ar savu piezīmju izvēli un pēc atskaņošanas pogas nospiešanas sintezators atskaņos katru noti pēc kārtas, līdz lietotājs vai nu nospiež pauzi, vai izvēlas.

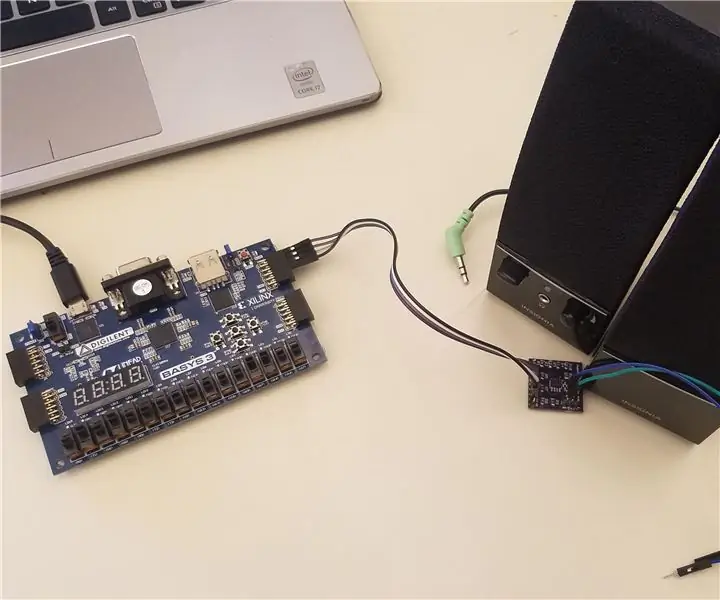

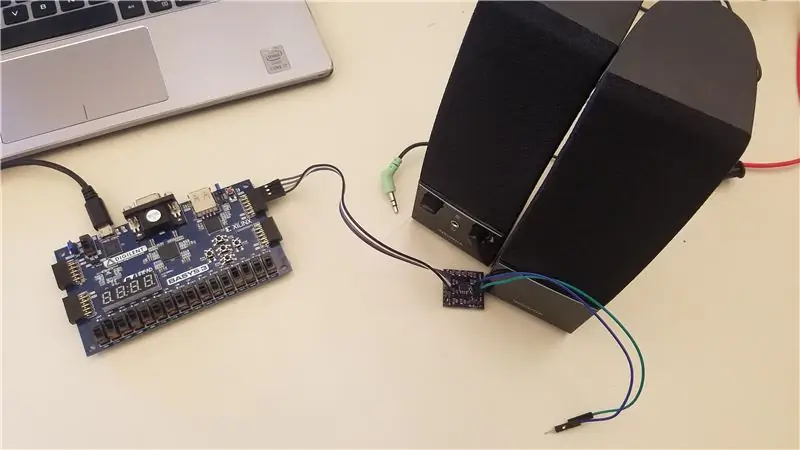

Šeit ir saraksts ar nepieciešamo aprīkojumu:

- Vivado (vai jebkura VHDL darba telpa)

- Basys 3 vai līdzīga FPGA plate

- Digitālā-analogā pārveidotājs (vismaz 4 biti)

- Skaļrunis ar austiņu ligzdu

- Vadu vadi

1. darbība. Digitālā sekvences lietotāja darbība

Tālāk ir norādītas darbības ar digitālo sekvencētāju. Digitālais sekvencētājs atbalsta 12 atšķirīgu skaņu atskaņošanu (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), kas svārstās no 261,6 Hz līdz 493,9 Hz.

1. Nospiediet kreiso pogu, lai ieslēgtu tāfeli atlases režīmā. Šajā režīmā katrs kreisais 4 slēdži (slēdži no 13 līdz 16) tiks izmantots, lai saglabātu atšķirīgu piķa vērtību.

2. Lai izdarītu atlasi, ieslēdziet vienu no kreisajiem slēdžiem un pēc tam izmantojiet labos 4 slēdžus (slēdži no 1 līdz 4), lai izvēlētos vēlamo soli. Laiks, kas saistīts ar konkrētu labo slēdžu kombināciju, tiks parādīts septiņu segmentu displejā, un displejs tiks atjaunināts uz jauno saistīto piķi, kad pareizie slēdži tiks pārvietoti uz jaunu kombināciju. Atpūtu var piešķirt, nekad nepiešķirot piķi vienam no kreisajiem slēdžiem, vai piezīmei piešķirot piķi, kas displejā parādīta kā 0. Kad vajadzīgais piķis ir atrasts un tiek parādīts displejā, nospiediet apakšējo piešķiršanas pogu, lai piezīmei piešķirtu šo konkrēto piķi.

3. Atkārtojiet 2. darbību attiecībā uz trim atlikušajām notīm, pagriežot katru atlikušo kreiso slēdzi atsevišķi, izvēloties attiecīgo slīpumu ar labajiem slēdžiem un nospiežot apakšējo pogu, lai piezīmei piešķirtu piķi. Vairākas piezīmes var piešķirt vienādam augstumam, vienlaikus pārvietojot uz augšu vairāk nekā vienu kreiso slēdzi.

4. Tagad, kad ir piešķirti visi piezīmju laukumi, digitālais sekvenceris ir gatavs atskaņošanai. Lai atskaņotu piezīmes skaļrunī, vienkārši nospiediet labo atskaņošanas/pauzes pogu, lai sāktu mūzikas atskaņošanu. Atskaņošanas secība no kreisās uz labo atspoguļo laukumus, kas saistīti ar kreisajiem slēdžiem. Piezīmes tiks atskaņotas ar noteiktu sitienu skaitu minūtē secībā 1, 2, 3, 4, 1, 2…. Displejā būs redzama piezīme, kas pašlaik tiek atskaņota, jo skaļruņi atskaņo mūziku. Lai apturētu mūzikas atskaņošanu, vienkārši nospiediet labo pogu, un tad mūzika tiks pārtraukta, un displejā tiks parādīts pauzes simbols. Vēlreiz nospiežot labo pogu, tiks atsākta atskaņošana.

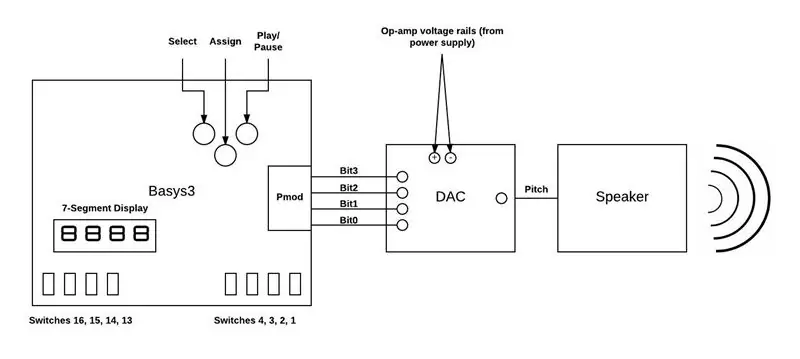

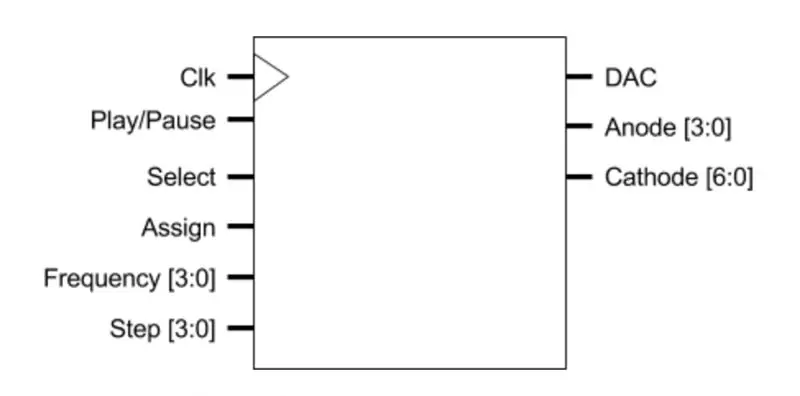

2. darbība. Tehniskā informācija

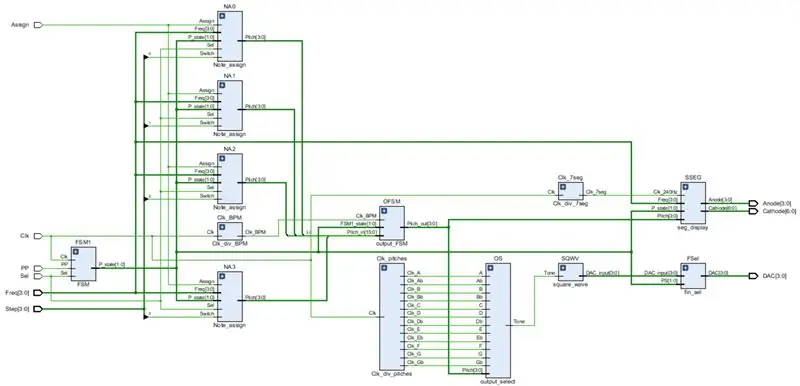

Mūsu sintezators izmanto daudzus dažādus digitālos komponentus. Iekļautas ierobežota stāvokļa mašīnas, reģistri, multipleksori, pulksteņu dalītāji un citi. Lai izveidotu mūsu sintezatoru, mēs izmantojām 10 unikālus moduļu failus. Tā vietā, lai katru moduli padarītu par sastāvdaļu, mēs sadalījām moduļu failus pēc funkcijas. Tā rezultātā lielākā daļa moduļu ir vairāk nekā viens komponents. Ņemiet vērā, ka iepriekš redzamais attēls parāda katru bloku, kas ir savienots kopā mūsu top dizainā.

Mēs apspriedīsim katru moduli, aprakstot ieejas un izejas, sadalot tā sastāvdaļas un izskaidrojot tā mērķi kopējā dizainā. Instrukcijas apakšā ir iekļauts ZIP fails, kas satur katru projektā izmantoto VHDL koda failu.

Ieejas

- Clk (dabiskais pulksteņa signāls)

- PP (atskaņošana/pauze)

- Sel (ievietojiet sintezatoru atlases režīmā)

- Piešķirt (piešķirt soli piķim)

- Solis (pozicionālās piezīmes)

- Freq (slēdži, kas rada vēlamo piķi)

Izejas

- Anods (7 segmentu anodi)

- Katods (7 segmentu katodi)

- DAC (4 biti, kas vada DAC)

3. darbība: tehniskā informācija

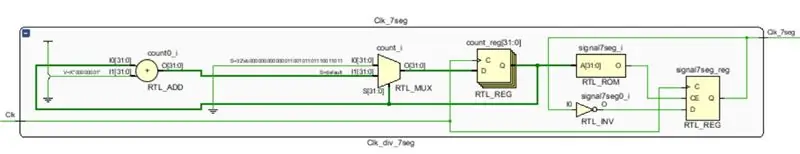

4. solis: 7 segmentu pulksteņu dalītājs

Mūsu sintezators izmanto trīs pulksteņa dalītājus, kas rada signālus, kas mūsu projektam kalpo citam mērķim. Pulksteņa dalītājs ņem sākotnējo pulksteņa signālu un rada mainītu signālu, kura frekvence ir mazāka par sākotnējo pulksteņa signālu. Basys 3 sākotnējais pulkstenis ir 100 MHz. Šī ir frekvence, ko izmanto mūsu pulksteņu dalītāji. Ja izmantojat citu FPGA plati ar atšķirīgu pulksteņa frekvenci, iespējams, būs jāmaina kods.

7 segmentu pulksteņa dalītājs rada signālu, kas vada seg_display failu. Mēs sīkāk paskaidrosim, kā šis fails darbojas, kad nokļūsim tā sadaļā. Būtībā šis pulksteņa dalītājs rada 240 Hz signālu, kas tiks izmantots, lai displejā pārslēgtos starp anodiem un katodiem. Signāls ir 240 Hz, jo frekvence, kādā cilvēka acs nevar atpazīt gaismas trūkumu, ir 60 Hz. Mēs izmantojam divus ciparus, tāpēc, dubultojot šo frekvenci, katrs cipars svārstīsies pie 60 Hz. Tad mēs to dubultojam, lai iegūtu 240 Hz, jo sistēma mainās tikai tad, kad signāls kļūst augsts, nevis tad, kad tas samazinās.

Lai to panāktu, dalītājs ņem dabisko 100 MHz signālu un skaita katru augšupejošo malu. Kad skaitītājs sasniedz 416667, izvade mainīsies no zemas uz augstu vai otrādi.

Ieejas

Clk (dabiskais pulksteņa signāls)

Izejas

Clk_7seg (līdz seg_display)

Sastāvdaļas

- D reģistrs

- MUX

- Invertors

- Papildinātājs

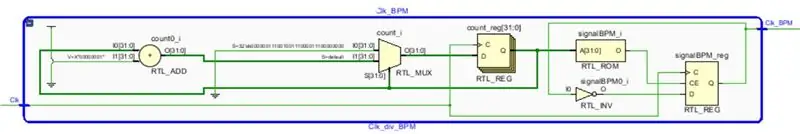

5. solis: sitieni minūtē pulksteņa dalītājs

BPM pulksteņa dalītājs darbojas līdzīgi. Šis dalītājs rada pulksteņa frekvenci, kas nodrošina pārslēgšanos starp četrām darbībām, kad atskaņošanas režīmā tiek izvadīti toņi. Mēs nolēmām pārslēgties starp piezīmēm ar ātrumu 100 BPM. Pie 100 BPM katra nots tiks atskaņota 3/5 sekundes. Iegūtā signāla frekvence būtu 1,67 Hz.

Lai radītu šādas frekvences signālu, mēs atkal izmantojām skaitīšanas sistēmu, taču šoreiz to skaits bija 60 miljoni. Katru reizi, kad skaitītājs sasniedza 60 miljonus, izejas signāls pārslēdzās augstu vai zemu.

Ieejas

Clk (dabiskā pulksteņa frekvence)

Izejas

Clk_BPM (uz output_FSM)

Sastāvdaļas

- D reģistrs

- MUX

- Invertors

- Papildinātājs

6. solis: pulksteņa dalītājs

Laukuma pulksteņu dalītājs ir lielākais no mūsu pulksteņu dalītājiem. Šis dalītājs izvada 12 dažādus signālus, kas atbilst 12 dažādām notīm, kuras var atskaņot mūsu sintezators. Izmantojot pamatzināšanas par mūzikas teoriju, mēs secinājām, ka bits vai autobuss var svārstīties ar ātrumu, kas atbilst mūzikas notu biežumam. Lai redzētu mūsu izmantotās frekvences, skatieties šeit. Mēs izmantojām ceturto piķu oktāvu.

Šeit tiek izmantota tā pati skaitīšanas sistēma. Konkrētās vērtības, ar kurām mēs rēķinājāmies, skatiet failā ar nosaukumu Clk_div_pitches.

Ieejas

Clk (dabiskā pulksteņa frekvence)

Izejas

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (uz izvades_izvēli)

Sastāvdaļas

- D reģistrs

- MUX

- Invertors

- Papildinātājs

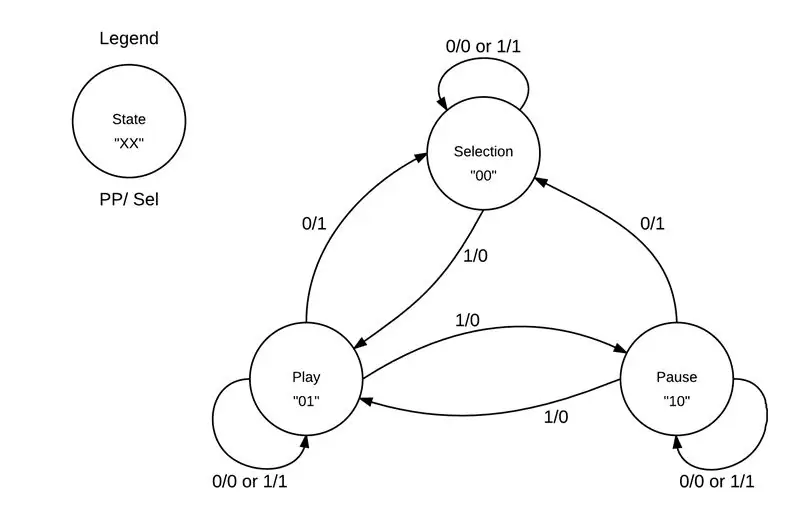

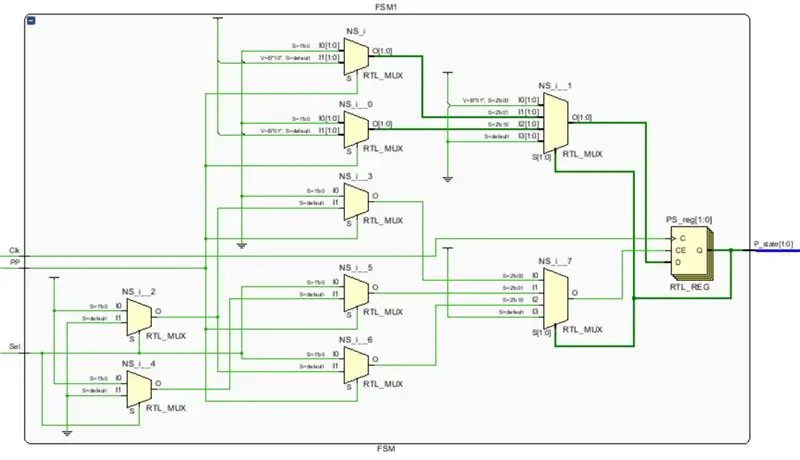

7. darbība: atskaņot/apturēt/atlasīt štata mašīnu

Mūsu projektā ir divas ierobežota stāvokļa mašīnas (FSM). MFV ir loģiska ierīce, kas var pastāvēt tikai vienā stāvoklī no ierobežota stāvokļu daudzuma. Izmantojot FSM, digitālā shēma var pāriet uz jaunu stāvokli, pamatojoties uz ievades kombināciju. Izmantojot ievades loģiku, FSM stāvoklis mainīsies, kad būs augoša pulksteņa mala. No stāvokļa un ievades ķēdē varat izveidot izvades loģiku, kas dod izejas, kas pastāv tikai tad, ja MFV ir noteiktā stāvoklī.

PPS stāvokļa mašīna ir pirmā FSM mūsu ķēdē. Šajā MFV ir trīs štati; Atskaņošanas, pauzes un atlases režīms. Lai pārvietotos pa dažādiem stāvokļiem, mēs izmantojām PP un atlases pogas. Skatiet iepriekšējo stāvokļa diagrammu, lai redzētu, kā notiek pārejas starp stāvokļiem. Mēs veicām šo FSM pāreju vietējā 100 MHz pulksteņa augšupejošajā malā, lai nebūtu iespējams, ka iekārta nepāriet, kad tiek nospiesta viena no pogām, pat ļoti īsu laiku. Pašreizējais stāvoklis (P_state) ir vienīgā izeja no šī moduļa.

Ieejas

- Clk (dabiskā pulksteņa frekvence)

- Sel (kreisā poga)

- PP (labā poga)

Izejas

P_state (pašreizējais stāvoklis, līdz output_FSM, note_assign, seg_dsiplay, final_select)

Sastāvdaļas

- MUX

- D reģistrs

8. darbība: atskaņot/apturēt/atlasīt štata mašīnu

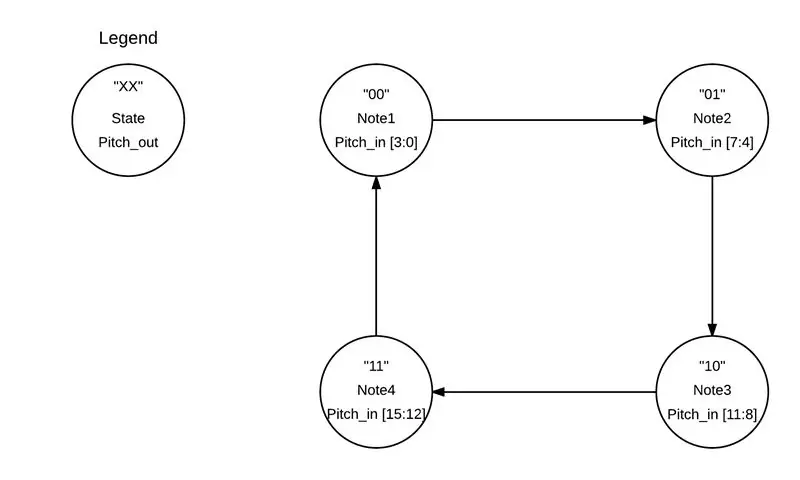

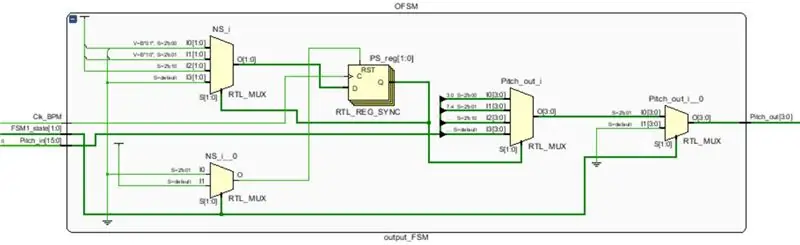

9. darbība: izvadiet FSM

Šī ir otrā MFV, uz kuru atsaucas iepriekšējā sadaļā. Šis MFV pilda citas funkcijas nekā otrs, taču pamatā tam ir viens un tas pats.

Izejas FSM darbojas tikai tad, ja pašreizējais stāvoklis no pirmā MFV ir "01" (atskaņošanas stāvoklis). Būtībā šī ir moduļa iespējošana. Ja stāvoklis ir "01", tad MFV gatavojas pārslēgties starp stāvokļiem BPM pulksteņa signāla augšupejošajā malā. Mēs to darām, jo output_FSM kontrolē, kurš izvēlētā piķa binārais numurs tiek nosūtīts uz moduļiem output_select un seg_display. MFV ir 16 bitu ievade, kas nāk no piezīmju piešķiršanas moduļa, kas tiks apskatīta tālāk. "00" stāvoklī output_FSM modulis izvadīs "xxxx" pirmajai piešķirtajai piezīmei. Pēc tam "01", tas tiks izvadīts "yyyy" otrajai notij un tā tālāk katrai notij, pirms atgriezīsieties pie pirmās piezīmes. Skatiet stāvokļa diagrammu iepriekš.

Šis MFV atšķiras no pirmā, jo nav ievades loģikas, lai kontrolētu pārslēgšanos starp stāvokļiem. Tā vietā MFV darbosies tikai tad, kad stāvoklis no pirmā MFV būs "01", un tad šī MFV pāries no stāvokļiem tikai uz pulksteņa signāla augšupejošās malas. Vēl viena atšķirība ir tāda, ka šim modulim ir izvades loģika, kas nozīmē, ka tas neizvada pašreizējo stāvokli, bet izvada piķa bināro skaitli šajā stāvoklī.

Ieejas

- Clk_BPM (BPM pulksteņa signāls no pulksteņa dalītāja)

- FSM1_state (PS no PPS FSM)

- Pitch_in (laukumi no piezīmju piešķiršanas)

Izejas

Pitch_out (viens piķis vienlaikus, lai izvadītu_selekciju un seg_display)

Sastāvdaļas

- MUX

- D reģistrs

10. darbība: izvadiet FSM

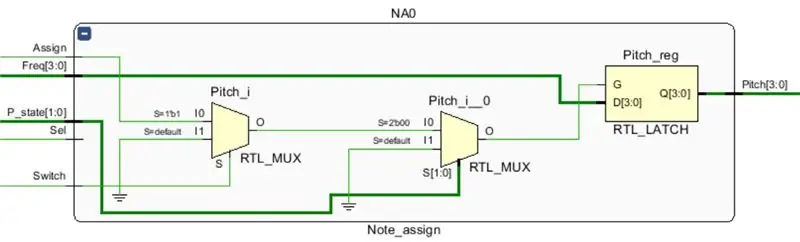

11. darbība. Piezīme Piešķirt

Piezīmju piešķiršanas modulis ir atbildīgs par augstuma piešķiršanu pozicionālajai piezīmei vai solim. Šis modulis patiesībā ir diezgan vienkāršs. Vispirms tiek pārbaudīts, vai ķēde ir "atlases" stāvoklī un vai pakāpienu slēdzis (tālu pa kreisi) ir augsts. Ja tā ir taisnība un tiek piespiesta piešķiršanas poga, moduļa izeja būs vienāda ar bināro skaitli, ko attēlo frekvences slēdži (labajā pusē).

Sākotnēji mēs mēģinājām izveidot moduli, kas faktiski saglabātu vienu no piķa pulksteņa signāliem izejā, taču mums radās problēmas, mainoties izejai, lai sekotu ieejas pulksteņa signāliem. Šis ir vienīgais modulis, ko vairāk nekā vienu reizi izmantoja gala projektā. Katrs solis ir saistīts ar piezīmju piešķiršanas moduli, un tāpēc katrs moduļa gadījums iegūst vienu bitu Step kopnes.

Ieejas

- P_state (pašreizējais stāvoklis no PPS FSM)

- Sel (kreisā poga)

- Slēdzis (viena soļa slēdzis)

- Frekvences (galēji labie slēdži)

- Piešķirt (apakšējā poga, piešķir piezīmi)

Izejas

Pitch (binārais skaitlis, uz output_FSM)

Sastāvdaļas

- MUX

- D reģistrējieties

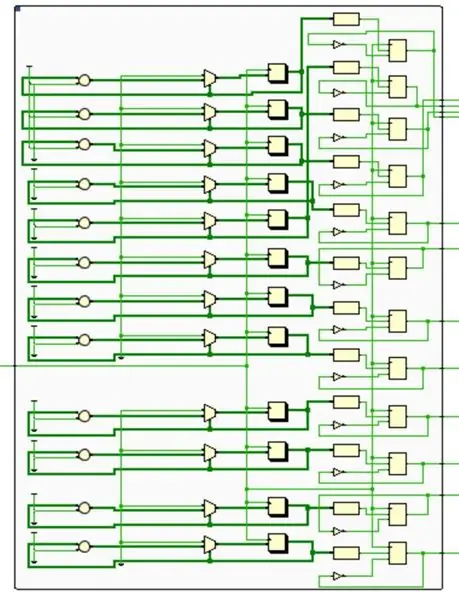

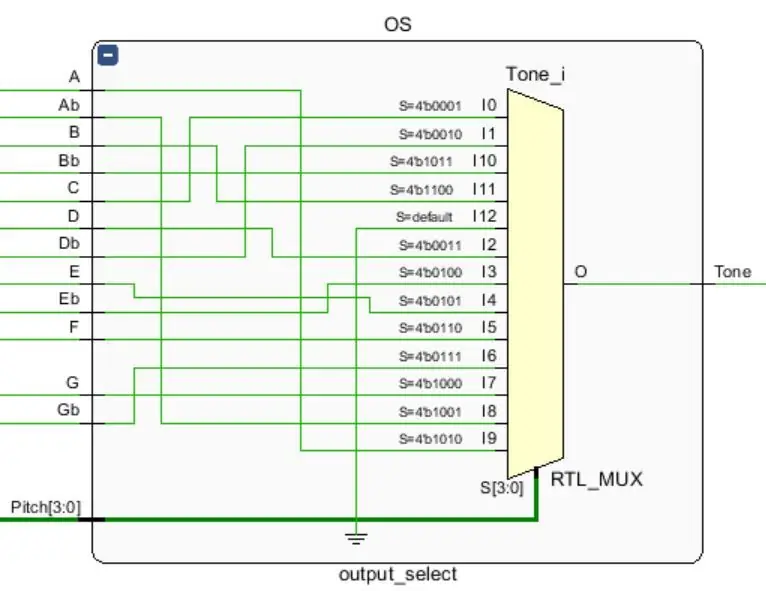

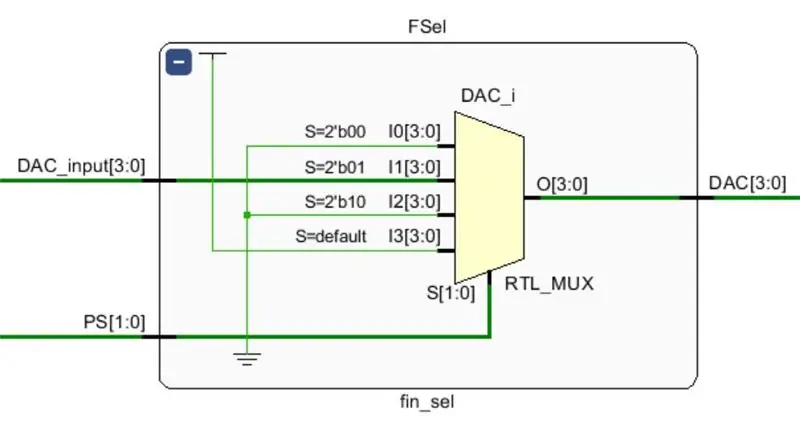

12. darbība: izvades izvēle

Izejas izvēle ir atbildīga par bināro skaitļu ņemšanu augstumam un savienošanu ar attiecīgo pulksteņa signālu. Neskatoties uz izmēru, tas ir arī salīdzinoši vienkāršs modulis. Output_select būtībā ir binārs dekodētājs, kas dekodē piķa bināro skaitli uz noteiktu pulksteņa signālu. Faktiski izejas piešķiršana pulksteņa frekvencei šeit darbojās labāk, salīdzinot ar moduli note_assign, jo šim modulim atlika tikai MUX pulksteņa signālus ar bināro skaitli, kas attēlo vadības ievadi.

Mēs atvainojamies par dīvaino maršrutēšanu, Vivado sakārtoja piķa signālus failam clk_div_pitches alfabētiskā secībā, bet šim failam tos sakārtoja pēc augoša bināra skaitļa, izraisot piķi citā secībā. Ņemiet vērā arī to, ka, ja binārais skaitlis no output_FSM bija "0000" vai kaut kas lielāks par "1100", tad MUX tika nosūtīts, izmantojot plakanu '0' signālu.

Ievadi

- Pitch (no output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (piķa pulksteņa signāli)

Izeja

Tonis (viens bits, kas atbilst izvēlētajam pulksteņa signālam, līdz kvadrātveida vilnim)

Sastāvdaļas

MUX

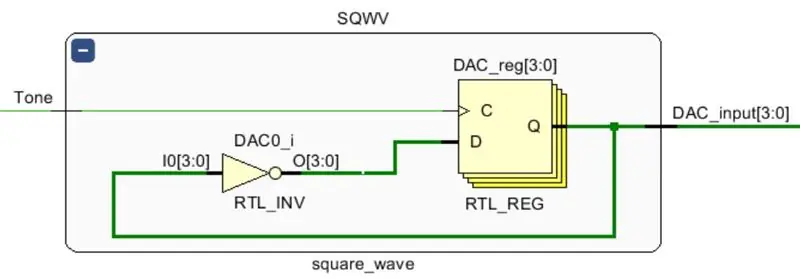

13. solis: Square Wave Gen

Modulis square_wave ir ģenerators kvadrātveida vilnim, kas tiek izvadīts no tāfeles uz DAC. Izmantojot signāla signālu no iepriekšējā faila, šis square_wave apgriež 4 bitu skaitli starp "0000" un "1111" Tone augošajā malā. Tonis ir īpaša piķa frekvence, tāpēc kvadrātveida vilnis rada viļņu ar citu frekvenci, kad output_FSM pāriet uz citu stāvokli. Šī moduļa 4 bitu izeja nonāk modulī fin_sel, kur loģika nosaka, vai šī kopne tiks izvadīta, pamatojoties uz stāvokli no PPS FSM.

Alternatīva šim kvadrātveida viļņu ģeneratoram rada sinusa vilni. Lai gan tas, visticamāk, radītu labāku gala toni, to ir ievērojami grūtāk īstenot, tāpēc mēs izvēlējāmies ģenerēt tikai kvadrātveida vilni.

Ieejas

Tonis (svārstīgs bits no output_select)

Izejas

DAC_input (svārstīga 4 bitu kopne, kas mainās ar tādu pašu signāla frekvenci)

Sastāvdaļas

- Invertors

- D reģistrs

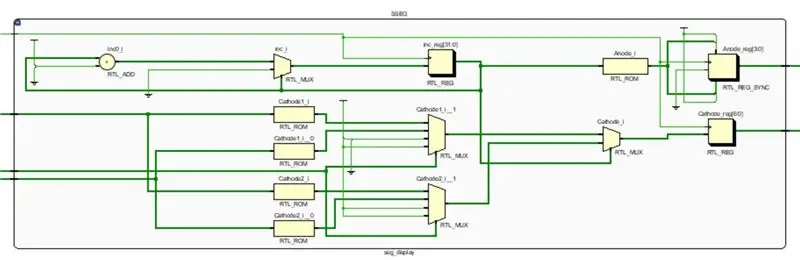

14. darbība: 7 segmentu displejs

Modulis seg_display kontrolē 7 segmentu displeju uz mūsu pamatplates. Moduļa ietvaros notiek divi procesi. Pirmais process atšifrē Freq, kad tas ir "atlases" stāvoklī, vai Pitch, kad tas ir "play" režīmā. "Pauzes" režīmā modulis atšifrē, lai parādītu pauzes simbolu. Aplūkojot VHDL kodu, jūs varat redzēt, ka binārais dekodētājs faktiski atšifrē ieeju divos dažādos signālos - katodā1 un katodā2. Katods1 apzīmē burtu, kas atbilst parādāmajam piķim, un katods2 apzīmē plakano simbolu (b), ja tāds ir. Iemesls tam ir saistīts ar otro seg_display moduļa veikto procesu.

Basys3 plāksnē segmenta displejā ir kopīgi katodi. Kamēr anodi kontrolē, kurš cipars ir ieslēgts, katodi kontrolē, kuri segmenti ir ieslēgti. Tā kā displejam ir kopīgi katodi, tas nozīmē, ka vienlaikus varat parādīt tikai vienu segmentu kopu. Tas rada problēmas šim projektam, jo mēs vēlamies vienlaikus parādīt burtu pie pirmā cipara un plakano simbolu, ja nepieciešams. Tagad atcerieties 7seg pulksteņa signālu? Lai apietu šo problēmu, mēs nomainām anodus un katodus uz priekšu un atpakaļ, izmantojot 7 segmenta signālu. Tā kā pulksteņa signāls ir 240 Hz un mēs izmantojam divus ciparus, katrs cipars svārstīsies ar 60 Hz frekvenci. Cilvēka acij izskatīsies, ka cipari nemaz nesvārstās.

Ņemiet vērā arī to, ka paneļa basys3 displejs izmanto negatīvu loģiku. Tas nozīmē, ka, ja anodam vai katodam ir iestatīta vērtība “0”, šis cipars vai segments būs ieslēgts un otrādi.

Ieejas

- Pitch (piezīmes binārais numurs, ko izmanto atskaņošanas stāvoklī)

- Frekvence (frekvences slēdži, tiek izmantoti atlases stāvoklī)

- P_state (pašreizējais stāvoklis no PPS FSM)

- Clk_240Hz (pulksteņa signāls no Clk_div_7seg, dubultā 120, jo mēs izmantojam tikai augošo malu)

Izejas

- Katods (kopne, kas kontrolē displeja segmentus, gala izvade)

- Anods (kopne, kas kontrolē ciparus displejā, gala izvade)

Sastāvdaļas

- Aizbīdnis

- MUX

- D reģistrs

15. solis: galīgā izvēle

Final select ir pēdējais šajā projektā izmantotais modulis. Vēl viens vienkāršs modulis, šis modulis kontrolē gala izvadi, kas tiks nosūtīts uz DAC. Kad režīms ir "atlases" vai "pauzes" stāvoklī, modulis izvadīs statisku "0000", lai mūzika netiktu atskaņota no skaļruņiem. "Play" stāvoklī modulis izvadīs svārstīgus 4 bitus, kā noteikts square_wave.

Ieejas

- P_state (pašreizējais stāvoklis no PPS FSM)

- DAC_input (svārstīgie 4 biti no square_wave)

Izejas

DAC (vienāds ar DAC_input atskaņošanas stāvoklī, gala izvade)

Sastāvdaļas

MUX

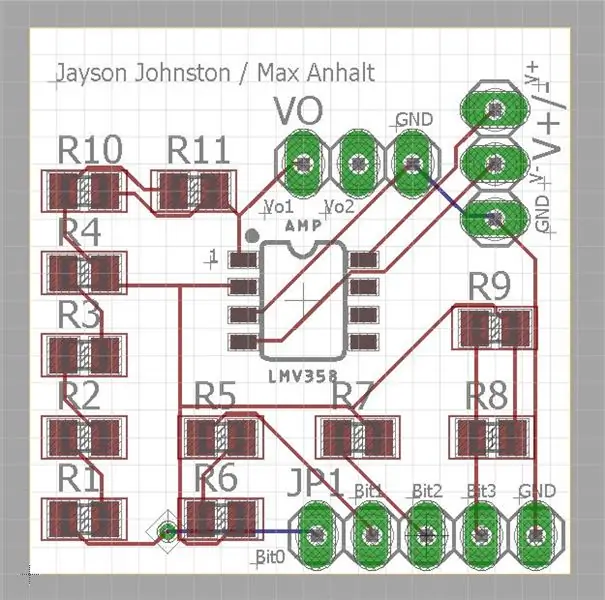

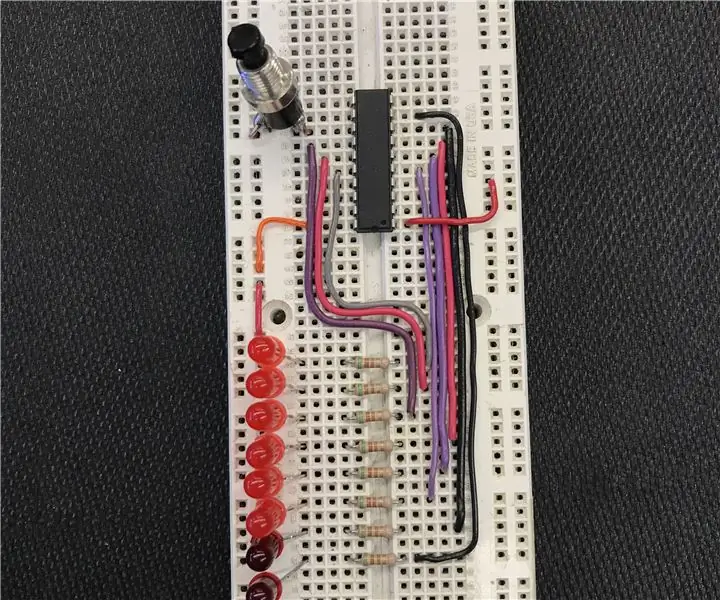

16. darbība. Ārējās ierīces: DAC

Digitālais analogo pārveidotājs (DAC) uztver diskrētu signālu un pārvērš to nepārtrauktā signālā. Mūsu DAC ir četri biti, un tas ir izgatavots no summēšanas pastiprinātāja. Izmantojot barošanas un atgriezeniskās saites cilpas rezistoru attiecību, mēs varējām izveidot sistēmu, kas izvada 16 dažādos līmeņos, veidojot, summējot katru filiāli. Bit0, augšējā filiāle, nes vismazāko svaru un nodrošina mazāko potenciālu, kad tas ir augsts, tāpēc zariem ir lielāka pretestība. Svars palielinās, ejot pa zariem. Ja skaitītu bināri uz augšu un pēc tam atpakaļ uz leju, izmantojot bitu ievadi, izejas spriegums izskatītos kā soli pa solim esošs sinusa vilnis. Ieeja DAC tika savienota ar vienu no tā dēļa PMOD, lai pārsūtītu 4 bitu signālu.

DAC sākotnēji tika samontēts elektrotehnikas klasei, un mēs to projektējām un lodējām, nevis nopirkām veikalā. Augšpusē ir dizaina faila attēls drukātās shēmas plates izveidošanai.

17. darbība. Ārējās ierīces: skaļrunis

Šim projektam jūs nevēlaties iegādāties super jauku skaļruņu pāri. Kā jūs varat pateikt, skaņa ir diezgan vienkārša. Mēs devāmies un nopirkām $ 8 datoru skaļruņu komplektu no Best Buy. Viss ar austiņu ligzdu darbojas labi. Monotons darbojas arī labi. Jūs pat varat izmantot austiņas, taču tās var izpūst!

Lai savienotu DAC izeju ar skaļruņiem, mēs izmantojām džemperu kabeļus un pēc tam turējām izejas kabeli pie austiņu ligzdas gala un zemējuma kabeli līdz pamatnei. Mēs mēģinājām izmantot elektrisko lenti, lai turētu kabeļus vietā, taču tas izraisīja daudz traucējumu. Izmēģinot cita veida lenti, varētu atrisināt šo problēmu.

Runājot par mūsu skaļruņiem, mēs tos pārslēdzām uz visaugstāko iestatījumu un saņēmām pienācīgi skaļu troksni.

Un tas ir pēdējais solis, lai izveidotu digitālo sekvencētāju no FPGA plates! Dodieties uz nākamajām divām sadaļām, lai lejupielādētu visu mūsu VHDL kodu un redzētu sekvenceri darbībā.

18. darbība. Video demonstrācija

Šis video parāda darba projekta galīgo versiju, ieskaitot slēdžu piešķiršanas procesu 4 atšķirīgiem laukumiem un skaļruņiem, kas atskaņo attiecīgās notis.

19. darbība: VHDL kods

Šeit ir visa projekta kods, ieskaitot ierobežojumus un sim failus, kas izmantoti, veidojot secību. Ņemiet vērā, ka neizmantotie dizaina faili to saka arhitektūrā.

Ieteicams:

Vienkāršs sekvencētājs: 16 soļi (ar attēliem)

Vienkāršs sekvenceris: Viena no labas mūzikas veidošanas atslēgām ir bezcerīga atkārtošana. Tas ir tas, ko vienkāršais sekvencētājs lieliski pārvalda. Tas atkal un atkal dara to pašu astoņu piezīmju secībā. Jūs varat pielāgot piezīmes biežumu, piezīmes ilgumu un

Alus sekvencētājs: 7 soļi

Alus sekvencētājs: Cos'èIl Beer Sequencer ir viens sekvenceris un nomierinošs solis attivabili tramite dei pesi. FSR (spēka sensoru rezistors) tiek izmantots, lai izmantotu detalizētu un mainīgu iespēju. La Variaz

Atari Punk konsole ar bērnu 8 soļu sekvencētājs: 7 soļi (ar attēliem)

Atari Punk konsole ar Baby 8 pakāpju sekvencētāju: šī starpposma konstrukcija ir viss vienā Atari Punk konsole un Baby 8 pakāpju sekvenceris, ko varat frēzēt ar Bantam Tools darbvirsmas PCB frēzmašīnu. To veido divas shēmas plates: viena ir lietotāja interfeisa (UI) plate, bet otra ir utilīta

Lokomotīves modelis ar soļu motoru vadību - Soļu motors kā rotācijas kodētājs: 11 soļi (ar attēliem)

Lokomotīves modelis ar soļu motoru vadību | Pakāpju motors kā rotācijas kodētājs: Vienā no iepriekšējām instrukcijām mēs uzzinājām, kā izmantot pakāpju motoru kā rotējošu kodētāju. Šajā projektā mēs tagad izmantosim šo pakāpju motoru pagriezto rotējošo kodētāju, lai vadītu lokomotīves modeli, izmantojot Arduino mikrokontrolleru. Tātad, bez fu

Gaismas sekvencētājs, izmantojot montāžu un mikroshēmu PIC16F690: 3 soļi

Gaismas sekvencētājs, izmantojot montāžu un mikroshēmu PIC16F690: Šī projekta mērķis ir izveidot gaismas sekvencētāju, lai pārbaudītu spēlētāja reakcijas ātrumu. Šī gaismas sekvences lietotāja interfeiss sastāv no 8 gaismas diodēm un pogas. No tehniskās puses mēs nosūtīsim kodu, kas rakstīts montāžas valodā, izmantojot