Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:53.

- Pēdējoreiz modificēts 2025-01-23 14:59.

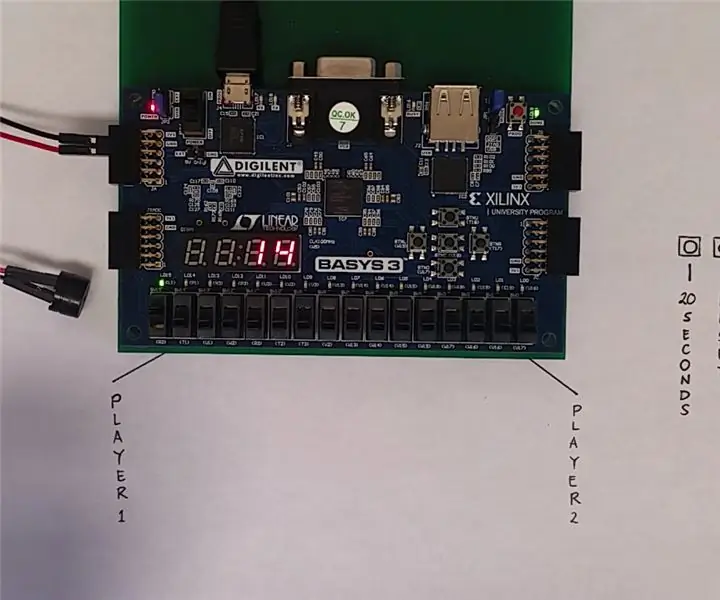

Šajā projektā izstrādātā konkurējošā zummeru sistēma darbojas līdzīgi zummeru sistēmām, kuras tiek izmantotas reģionālajos un nacionālajos zinātnes bļodas konkursos. Šo projektu iedvesmoja mana līdzdalība manas vidusskolas zinātnes bļodas komandā trīs gadus. Mums vienmēr ir bijusi vēlme atjaunot bloķēšanas signālu sistēmu ar 5 sekunžu un 20 sekunžu taimeri.

Lai sniegtu sīkāku informāciju par skaņas signālu sistēmu, zinātniskās bļodas skaņas signāli ir ieprogrammēti, lai ievadītu ne vairāk kā 8 spēlētājus (ar 8 atsevišķiem skaņas signāliem). Kad viens skaņas signāls ir nospiests, pirmās personas skaņas signāls iedegsies, norādot, kurš spēlētājs saņem jautājumu. Pārējie spēlētāji tiks "izslēgti", kas nozīmē, ka viņu skaņas signāli nereaģēs, kamēr moderators neatiestatīs skaņas signāla sistēmu.

Kad moderators būs izlasījis jautājumus, viņš nospiedīs pogu, lai sāktu atpakaļskaitīšanas taimeri, kas tiks parādīts septiņu segmentu displejā. Pēc jautājuma “uzmešana” moderators var nospiest labo pogu, lai sāktu atpakaļskaitīšanu no 5 sekundēm. Tikmēr pēc "bonusa" jautājuma moderators var nospiest kreiso pogu, lai sāktu atpakaļskaitīšanu no 20 sekundēm. Kad taimeris sasniegs nulli, skaņas signāls norādīs, ka atskaņotājam ir beidzies laiks.

Lai atiestatītu sistēmu un atpakaļskaitīšanas taimeri, moderators var nospiest centrālo pogu. Lai atiestatītu bloķēšanas mehānismu un atskaņotāja gaismas diodes, 1. un 2. atskaņotāja slēdžiem jābūt zemiem.

1. solis: materiāli

Jums būs nepieciešams:

- Basys3 plate (vai līdzvērtīga FPGA plate)

- Micro-B USB kabelis

- Skaļrunis (es izmantoju pasīvo skaļruni)

- 2 vadi

- Programmatūra, ko ieviest FPGA (es izmantoju Vivado)

- Konkurētspējīgas skaņas signālu sistēmas fails

2. solis: Melnās kastes diagramma

Melnās kastes diagramma parāda ieejas un izejas, kas tiks izmantotas šajā signālu sistēmā.

IEVADES:

player1, player2 Šīs ieejas ir savienotas ar diviem slēdžiem uz Basys3 plates. Ērtības labad tiks izmantoti kreisie un labie slēdži.

atiestatīšana Centrālā poga tiks izmantota, lai attēlotu atiestatīšanas pogu.

count_down_20_sec Kreisā poga tiks izmantota, lai attēlotu 20 sekunžu taimera pogu.

count_down_5_sec Labā poga tiks izmantota, lai attēlotu 20 sekunžu taimera pogu. Lai nodrošinātu, ka tiek iedarbināts gan 20 sekunžu, gan 5 sekunžu taimeris, turiet pogu nospiestu, līdz septiņu segmentu displejā tiek parādīts taimeris.

CLK FPGA plate ģenerēs pulksteni, kas darbojas ar 10 ns frekvenci.

Izejas:

skaļrunis Skaļruņu izeja ir pievienota ārējam skaņas signālam vai skaļrunim. Jums būs jāpievieno skaļrunis Basys3 plates JA pmod portiem. Šis solis tiks aprakstīts zemāk.

speaker_LED Šī izeja ir savienota ar gaismas diodi tāfeles centrā, un tā tikai norādīs, kad FPGA skaļruņu jauda ir augsta. To var izmantot, lai pārbaudītu ārējo skaļruni. Ņemiet vērā, ka daži pmod porti var nedarboties labi, tāpēc varat izmēģināt dažādus portālus un izmantot LED, lai pārbaudītu, vai skaļrunim jābūt ieslēgtam.

SEGMENTI Šī izvade ir savienota ar astoņiem atsevišķiem segmentiem septiņu segmentu displejā, ieskaitot decimāldaļu.

DISP_LV Šī izeja ir savienota ar četriem septiņu segmentu displeja anodiem.

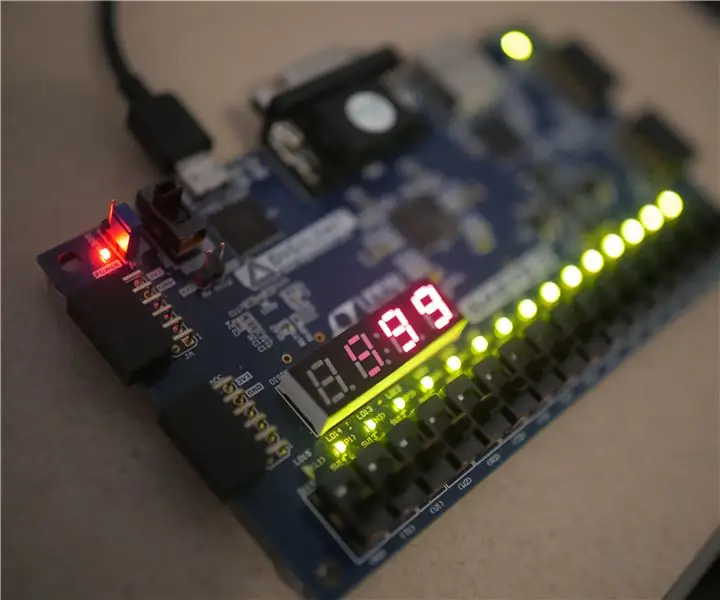

player_LED Šī izeja ir divu saišu signāls, kas ir savienots ar gaismas diodēm virs atskaņotāja1 un atskaņotāja2 slēdžiem. Pirmais spēlētājs, kurš pagrieza atbilstošo slēdzi, tiks norādīts ar gaismas diodi. Ņemiet vērā, ka abas gaismas diodes nevar ieslēgties vienlaicīgi.

3. darbība: ārējā skaļruņa pievienošana

Lai savienotu ārējo skaļruni ar Basys3 plati, paņemiet divus vadus un pievienojiet tos, kā norādīts iepriekš redzamajā attēlā. Baltā līnija savieno skaļruņa negatīvo spaili ar paneļa zemējuma portu. Sarkanā līnija savieno skaļruņa pozitīvo spaili ar paneļa JA10 pmod portu.

Ierobežojumu fails ir veidots tā, lai jebkuram portam no JA1 līdz JA10 būtu jāstrādā. Tomēr daži tapas uz tāfeles ir nereaģējoši, tādēļ, ja JA10 nedarbojas, varat izmēģināt citus portus.

4. solis: strukturālā diagramma

Iepriekš redzamajā attēlā redzama konkurējošās zummeru sistēmas strukturālā shēma, ieskaitot visas sastāvdaļas, kas veido galveno moduli. Viņu apraksti ir šādi:

player_lockout_LED1 Spēlētāja bloķēšanas LED komponents ir ierobežota stāvokļa iekārta, kas izmanto vienas karsta kodējumu. Tam ir četras ieejas: player1, player2, reset un CLK. Tajā ir 2 bitu komplekta izvades atskaņotājs_LED. Komponenta player_lockout_LED1 ieejas un izejas ir tieši savienotas ar identiski nosauktajām galvenā moduļa ieejām un izejām.

buzzer_tone1 Buzzer komponents ir balstīts uz šo forumā ievietoto kodu

stackoverflow.com/questions/22767256/vhdl-… Tomēr tas tika pārveidots, lai izvadītu nepārtrauktu skaņu ar frekvenci 440 Hz (piezīme). Iespējošanas ievade ir pievienota signālam buzzer_enable, kas ir komponenta down_counter_FSM1 izeja.

clk_div1 Pulksteņa dalītāja sastāvdaļa ir profesora Braiena Mīlija pulksteņa dalītāja modificētā versija, kas pieejama vietnē PolyLearn. Tas palēnina pulksteņa darbību, tāpēc izvades periods ir 1 sekunde.

down_counter_FSM1 Lejupejošais skaitītājs ir FSM, kas paredzēts atpakaļskaitīšanai līdz nullei. Divi iespējamie sākuma laiki ir 20 vai 5, kurus izvēlas lietotāja ievade. Kad taimeris ir sasniedzis nulli, tas izvada '1', norādot, ka laiks ir beidzies. Šī izeja darbojas kā signāla signāla komponenta iespējošanas līdzeklis. Skaitītājs arī izvada 8 bitu saišķa signālu, kas nosūta 8 bitu BCD, kas tiek nosūtīts uz segmenta dekodētāju. Vēl viena izeja ir skaitītājs_on, kas arī ir savienots ar derīgo segmenta dekodētāja ievadi.

sseg_dec1 Septiņu segmentu dekodētāja komponents ir pieejams vietnē PolyLearn, un to uzrakstīja profesors Braiens Mīlijs. Tas izmanto BCD ievadi, ko nodrošina down_counter_FSM1, un izvada decimālo ekvivalentu septiņu segmentu displejā. Kad skaitītājs ir ieslēgts, derīgā vērtība ir augsta. Tas ļauj dekodētājam parādīt decimālo skaitli septiņu segmentu displejā. Kad skaitītājs ir izslēgts, derīgā ievade ir zema. Septiņu segmentu displejā būs redzamas tikai četras domuzīmes.

5. solis: Galīgā stāvokļa mašīnas (FSM) diagramma

Galīgo iekārtu jutīguma sarakstā ir atskaņotājs1, spēlētājs2, atiestatīšana un pulkstenis. FSM izeja ir 2 bitu komplekta atskaņotājs_LED, kas savienots ar divām gaismas diodēm uz Basys3 plates. Galīgā stāvokļa mašīna parāda šādus trīs stāvokļus:

ST0 ir sākuma stāvoklis. Šajā stāvoklī abas gaismas diodes tiek izslēgtas. MFV paliks šajā stāvoklī, ja spēlētājs1 un spēlētājs2 būs zemi. Asinhronā atiestatīšana arī nosaka stāvokli ST0. Kad atskaņotāja1 slēdzis ir iestatīts uz augstu, nākamais stāvoklis būs ST1. Ja atskaņotāja2 slēdzis ir iestatīts uz augstu, nākamais stāvoklis būs ST2.

ST1 ir stāvoklis, kurā ir ieslēgta atskaņotāja1 gaismas diode. MFV paliks šajā stāvoklī jebkurai ievadei. Tas nozīmē, ka pat tad, kad atskaņotājs2 slēdzis ir iestatīts augstā stāvoklī uzreiz pēc tam, kad atskaņotājs1 slēdzis ir augsts, tas paliks ST1. Tikai asinhronā atiestatīšana var iestatīt nākamo stāvokli uz ST0.

ST2 ir stāvoklis, kurā ir ieslēgta atskaņotāja2 gaismas diode. Līdzīgi kā ST!, FSM paliks šajā stāvoklī jebkurai ievadei, pat ja atskaņotājs1 slēdzis ir iestatīts augstā stāvoklī tūlīt pēc tam, kad atskaņotāja2 slēdzis ir augsts. Atkal tikai asinhronā atiestatīšana var iestatīt nākamo stāvokli uz ST0.

Ieteicams:

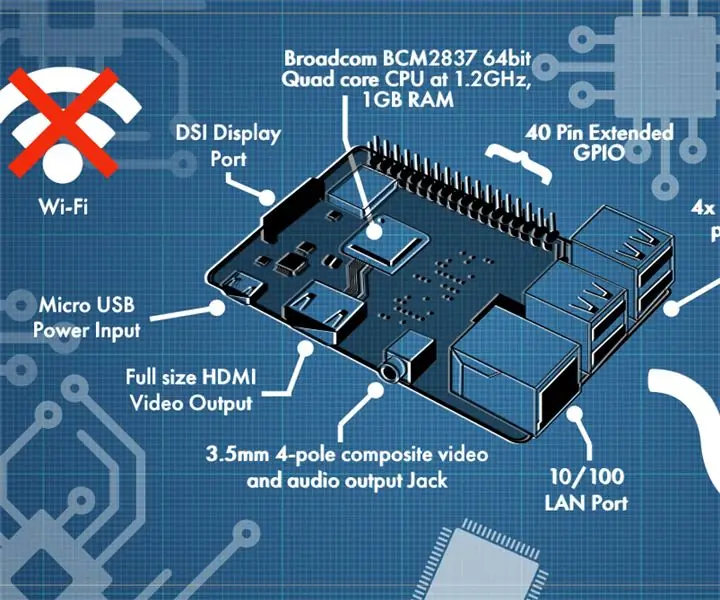

Īpaši mazjaudas WiFi mājas automatizācijas sistēma: 6 soļi (ar attēliem)

Īpaši mazjaudas WiFi mājas automatizācijas sistēma: Šajā projektā mēs parādām, kā dažās darbībās varat izveidot pamata vietējo mājas automatizācijas sistēmu. Mēs izmantosim Raspberry Pi, kas darbosies kā centrālā WiFi ierīce. Tā kā gala mezgliem mēs izmantosim IOT kriketu, lai izveidotu akumulatora enerģiju

Rēķinu norēķinu un krājumu kontroles sistēma: 3 soļi

RĒĶINU RĒĶINU UN KRĀJUMU VADĪBAS SISTĒMA: Izmantojot šo pamācību, es sniegšu jums ideju izveidot rēķinu un inventāra kontroles sistēmu. Izmantojot MS piekļuvi. Tas ir ļoti vienkārši, un jums nav vajadzīgas papildu zināšanas par datoru vai programmēšanu. Ja jums ir pamatzināšanas par kundzi Piekļuve, tabulas. veidlapas un atskaites

Arduino brīdinājuma sistēma par automašīnas novietošanu atpakaļgaitā Soli pa solim: 4 soļi

Arduino brīdinājuma sistēma par automašīnas novietošanu atpakaļgaitā Soli pa solim: Šajā projektā es izveidošu vienkāršu Arduino automašīnas atpakaļgaitas stāvvietas sensora shēmu, izmantojot Arduino UNO un ultraskaņas sensoru HC-SR04. Šo uz Arduino bāzēto automašīnas reverso brīdinājuma sistēmu var izmantot autonomai navigācijai, robotu diapazonam un citiem diapazoniem

Krāsu šķirošanas sistēma: Arduino balstīta sistēma ar divām jostām: 8 soļi

Krāsu šķirošanas sistēma: Arduino balstīta sistēma ar divām jostām: Produktu un priekšmetu transportēšana un/vai iepakošana rūpniecības jomā tiek veikta, izmantojot līnijas, kas izgatavotas, izmantojot konveijera lentes. Šīs jostas palīdz ar noteiktu ātrumu pārvietot priekšmetu no viena punkta uz otru. Daži apstrādes vai identifikācijas uzdevumi var būt

2 spēlētāju konkurētspējīga VS laika noteikšanas spēle: 4 soļi

2 spēlētāju konkurētspējīga spēles laika noteikšanas spēle: Jums būs nepieciešams: 1.Digilent Basys 3, FPGA padome (vai jebkura cita FPGA) Salīdzinoši atjaunināta Vivado versija vai kāda cita VHDL vide3. Dators, kas spēj palaist minēto programmu