Satura rādītājs:

- 1. darbība: PWM moduļa avota faila izveide

- 2. solis: PWM moduļa izveide- Vivado iestatīšana

- 3. solis: PWM moduļa izveide- izveidojiet projekta failu

- 4. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (I)

- 5. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (II)

- 6. darbība: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (III)

- 7. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (IV)

- 8. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (V)

- 9. solis: PWM moduļa izveide- aparatūras uzstādīšana

- 10. darbība. PWM moduļa izveide- ģenerējiet bitu plūsmu un palaidiet SDK

- 11. darbība: PWM moduļa izveide- izveidojiet jaunu lietojumprogrammu Xilinx SDK

- 12. solis: PWM moduļa izveide- Project Explorer pārskats (I)

- 13. darbība. PWM moduļa izveide- Project Explorer pārskats (II)

- 14. solis: PWM moduļa izveide- Project Explorer pārskats (III)

- 15. solis: PWM moduļa izveide- iesaiņojiet PWM funkciju (I)

- 16. solis: PWM moduļa izveide- iesaiņojiet PWM funkciju (II)

- 17. solis: PWM moduļa izveide- iesaiņojiet PWM funkciju (III)

- 18. solis: PWM moduļa izveide- palaidiet to

- 19. darbība: video straumēšanas straumēšana Digilent ZYBO, izmantojot OV7670

- 20. solis: aizpildiet bloka diagrammu

- 21. darbība: pievienojiet OV7670 ZYBO

- 22. darbība: izveidojiet bloka dizainu

- 23. darbība: pievienojiet VHDL failus OV7670 kameras vadībai un uzņemšanai

- 24. darbība: pievienojiet ierobežojumu failu

- 25. darbība: pievienojiet IP Repo HLS IP

- 26. darbība: pievienojiet moduļus un IP

- 27. darbība: IP konfigurācijas iestatījumi

- 28. darbība: pievienojiet un konfigurējiet PS IP bloku

- 29. solis: 1. daļa. PWM moduļa izveide servomotoriem

- 30. darbība: video ievades sānu savienojumi (iezīmēts aclk)

- 31. darbība: savienojumi ar OV7670

- 32. darbība. Savienojumi video izejas pusē

- 33. darbība: palaidiet bloķēšanas un savienojuma automatizāciju

- 34. darbība: izveidojiet HDL iesaiņojumu

- 35. solis: ģenerējiet bitu plūsmu, eksportējiet aparatūru uz SDK, palaidiet SDK no Vivado

- 36. darbība: SDK (bez FreeRTOS)

- 37. solis: FreeRTOS ieviešana

- 38. solis: lietošanas instrukcijas

- 39. darbība: atsauces un saites

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:57.

- Pēdējoreiz modificēts 2025-01-23 14:59.

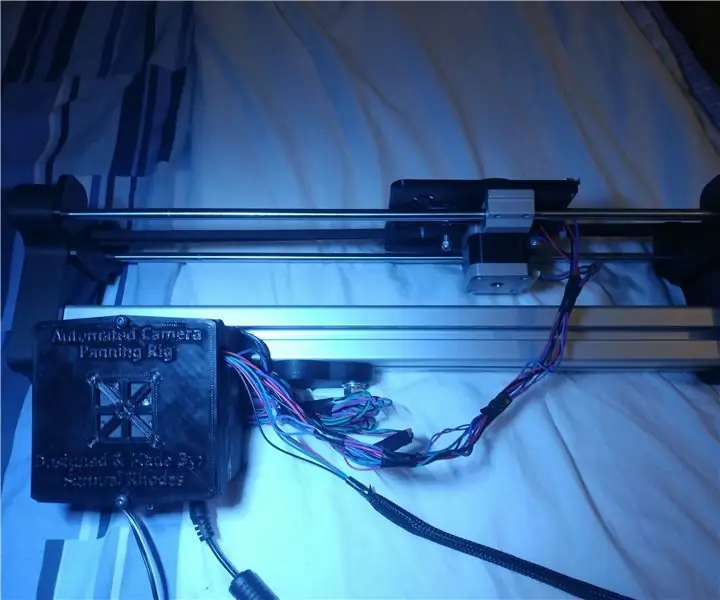

Sāciet ar pirmo soli, lai iegūtu sīkāku informāciju par 2 asu servo PWM kontrollera izveidi.

Sāciet ar masveida bloka diagrammu (19. darbība) visam projektam.

Kameras + panoramēšanas/noliekšanas iestatījumi, kurus mēs izmantojām:

Servo savienošanai tika izmantots PmodCON3 no Digilent.

1. darbība: PWM moduļa avota faila izveide

2. solis: PWM moduļa izveide- Vivado iestatīšana

Vispirms lejupielādējiet Vivado Design Suite no Xilinx vietnes. Instalējiet visu dizaina komplektu, ieskaitot Vivado programmatūras izstrādes komplektu (SDK). Šis projekts izmanto versiju 2017.2.

Tikmēr Digilent Adept 2 ir jāinstalē arī kā Zybo plates draiveris.

3. solis: PWM moduļa izveide- izveidojiet projekta failu

Pirms projekta faila izveides jums jāpārliecinās, vai esat jau pareizi instalējis Zybo failu kā apmācību šeit:

Vivado versija 2015.1 un jaunāka plates failu instalēšana

Atveriet Vivado 2017.2. Ātrajā startā noklikšķiniet uz Izveidot projektu -> Tālāk -> Projekta nosaukums (nosauciet šeit sava projekta nosaukumu) -> Projekta veids. Sadaļā Projekta veids atlasiet RTL projekts un atzīmējiet uz “Nenorādīt avotus šobrīd”. Pēc tam noklusējuma daļai kā parādāmo nosaukumu izvēlieties “Dēļi” un “Zybo”. Pēc tam noklikšķiniet uz Pabeigt, lai sāktu projektu.

4. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (I)

Plūsmas navigatorā noklikšķiniet uz “Izveidot bloka dizainu”, pēc tam nospiediet Labi. noklikšķiniet uz “+” zīmes, lai pievienotu nepieciešamos IP. Pievienot:

- Viena ZYNQ7 apstrādes sistēma Divi AXI taimeris

- Divi AXI taimeris

5. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (II)

Pēc IP pievienošanas palaidiet bloķēšanas automatizāciju un savienojumu automatizāciju. Kad automatizācija ir pabeigta, blokā “axi_timer_0” ar peles labo pogu noklikšķiniet uz pwm0 -> Make External. Nosauciet pwm0 ārējo tapu kā pwm_Xaxis. Tāpat atkārtojiet iepriekš minēto procesu blokā “axi_timer_1” un nosauciet pwm0 ārējo tapu kā pwm_Zaxis.

6. darbība: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (III)

Ņemiet vērā, ka katru reizi, kad pabeidzam bloku dizainu Vivado, mums ir jāizveido HDL iesaiņojums. Tā kā tas būs katra projekta augstākā līmeņa modulis.

7. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (IV)

Tagad mums ir jāiestata ierobežojumu fails, lai piešķirtu tapas, kas savienotas ar mūsu blokshēmu. Aizveriet logu Bloķēt noformējumu, cilnē Avoti, “Pievienot avotus”-> Pievienojiet vai izveidojiet ierobežojumus-> pievienojiet Zybo-Master.xdc kā mūsu ierobežojumu failus.

8. solis: PWM moduļa izveide- bloku dizains un ierobežojumu failu iestatīšana (V)

Atveriet ierobežojumu failu Zybo-Master.xdc mapē Ierobežojumi, noņemiet komentārus par portiem, kurus vēlamies norādīt kā izejas signālus, un pārdēvējiet “get_ports {XXXX}”, kas XXXX apzīmē bloķēšanas diagrammā norādīto ārējo tapu. Ierobežojuma faila iestatījums ir parādīts attēlā.

9. solis: PWM moduļa izveide- aparatūras uzstādīšana

Pievienojiet servomotorus Pmod CON3. TowerPro SG90 ir servomotoru modelis, ko izmantojām šajā projektā. Servomotoru vadiem oranžais vads apzīmē PWM signālu, kas savienots ar SIG tapu Pmod CON3. Sarkanais vads Vcc ir barošanas vads, kas savienots ar VS tapu Pmod CON3. Visbeidzot, brūnais vads Gnd ir zemējuma vads, kas savienots ar GND tapu. Pēc tam ievietojiet Pmod CON3 Zybo Board augšējā JD porta rindā.

10. darbība. PWM moduļa izveide- ģenerējiet bitu plūsmu un palaidiet SDK

1. Cilnē Project Navigator palaidiet Izveidot BitStream.

2. Eksportēt aparatūru: Fails> Eksportēt> Eksportēt aparatūru-> atzīmējiet “iekļaut bitu plūsmu”-> Labi 3. Sākt SDK: Fails-> Uzsākt SDK.

11. darbība: PWM moduļa izveide- izveidojiet jaunu lietojumprogrammu Xilinx SDK

Izveidojiet jaunu lietojumprogrammu:

Fails> Jauns> Lietojumprogrammas projekts -> Ievadiet sava projekta nosaukumu -> Pabeigt

Sadaļā Project Explorer jābūt trim mapēm.

Šajā gadījumā “design_1_wrapper_hw_platform_0” ir mape, kuru Vivado iepriekš eksportēja. Axis_2_PWM_SDK_bsp ir tāfeles atbalsta pakotnes mape. Axis_2_PWM_SDK ir mūsu galvenā projekta mape SDK. Failu “helloworld.c” varat redzēt Axis_2_PWM_SDK mapē “src”, kur “helloworld.c” ir galvenais fails.

12. solis: PWM moduļa izveide- Project Explorer pārskats (I)

Pārbaudīsim dažus failus programmā Project Explorer. Vispirms mapē “design_1_wrapper_hw_platform_0” atveriet “system.hdf”. Šis fails parāda procesora ps7_cortex9 adrešu karti un mūsu dizainā esošos IP blokus.

13. darbība. PWM moduļa izveide- Project Explorer pārskats (II)

Pēc tam mapē “Axis_2_PWM_SDK_bsp” pārbaudiet “include” un “libsrc” failus. Bibliotēkas faili šeit ļauj mums mijiedarboties ar aparatūras perifērijas ierīcēm, “nespēlējot” reģistrus.

14. solis: PWM moduļa izveide- Project Explorer pārskats (III)

Izmantojot BSP dokumentāciju, xtmrctr.h ir atrodama kā Xilinx taimera vadības bibliotēka, kas saistīta ar AXI taimeri. Parasti šeit mēs varētu atrast vēlamo PWM funkciju. Tomēr, izlasot dokumentāciju “tmrctr_v4_3”, tas parāda, ka draiveris pašlaik neatbalsta ierīces PWM darbību. PWM funkcijas trūkuma dēļ mums ir jāapkopo mūsu PWM funkcija, izmantojot xtmrctr.h un AXI Timer v2.0 LogiCORE IP produktu rokasgrāmatu.

15. solis: PWM moduļa izveide- iesaiņojiet PWM funkciju (I)

Atgriežoties pie galvenā faila “helloworld.c”, iekļaujiet šādus galvenes failus:

16. solis: PWM moduļa izveide- iesaiņojiet PWM funkciju (II)

Definējiet divu AXI TImer bāzes adreses, izmantojot “xparameters.h”.

17. solis: PWM moduļa izveide- iesaiņojiet PWM funkciju (III)

Izveidojiet vēlamo PWM funkciju.

Duty_val: pārvērš pakāpes vērtību darba ciklā. PWM_Freq_Duty: iestatiet vēlamo frekvenci un darba ciklu, lai ģenerētu PWM. Jāpiešķir arī pulksteņa periods.

PWM_START: piešķiriet PWM reģistra adresi un sāciet ģenerēt PWM.

PWM_STOP: piešķiriet PWM reģistra adresi un pārtrauciet PWM ģenerēšanu.

Pārējais demonstrācijas kods ir redzams sadaļā “helloworld.c” sadaļā “Axis_2_PWM_SDK”

18. solis: PWM moduļa izveide- palaidiet to

1. Programmējiet FPGA, izmantojot SDK

- Savienojiet Zybo Board ar datoru, izmantojot USB portu.

- Xilinx rīki -> Programmēt FPGA

2. Palaidiet programmu

Noklikšķiniet uz ikonas “Palaist” un nolaižamajā izvēlnē -> Palaist kā -> Uzsākt aparatūrā

3. SDK terminālis

- Atveriet SDK termināli -> Pievienoties seriālajam portam -> Labi

- Palaidiet programmu. Ja demonstrācijas kods darbojas veiksmīgi, jums vajadzētu redzēt “Inicializācija pabeigta!” SDK terminālī.

19. darbība: video straumēšanas straumēšana Digilent ZYBO, izmantojot OV7670

Pilns arhīva fails pievienots.

20. solis: aizpildiet bloka diagrammu

Tas parāda visu projekta savienojumu un IP bloku pilnu shēmu

21. darbība: pievienojiet OV7670 ZYBO

Izveidojiet savienojumu, lai savienotu ov7670 moduli ar ZYBO Pmods

Dati Pmod ir Pmod D

Kontroles Pmod ir Pmod C

Turklāt pievienojiet PmodCON3 un servos, kā norādīts šīs apmācības pirmajā pusē

22. darbība: izveidojiet bloka dizainu

Plūsmas navigatorā noklikšķiniet uz "Izveidot bloka dizainu", pēc tam nospiediet Labi.

23. darbība: pievienojiet VHDL failus OV7670 kameras vadībai un uzņemšanai

Pievienojiet šim solim pievienotos VHDL failus projektam

24. darbība: pievienojiet ierobežojumu failu

Pievienojiet savam projektam pievienoto ierobežojumu failu.

25. darbība: pievienojiet IP Repo HLS IP

Paņemiet pievienoto Zip failu un izpakojiet to jaunā mapē ar nosaukumu līdzīgi jaunā direktorijā (mapē) ar nosaukumu "HLS_repo".

Pievienojiet savam projektam IP krātuvi, dodoties uz IP katalogu un ar peles labo pogu noklikšķinot uz "Pievienot repozitoriju …"

Dodieties uz direktoriju "HLS_repo" un atlasiet to.

Pēc izvēles: izveidojiet sev HLS video apstrādes bloku!

26. darbība: pievienojiet moduļus un IP

Pievienojiet moduļus ov7670_axi_stream_capture, debounce un ov7670_controller blokdiagrammai, ar peles labo pogu noklikšķinot uz fona un atlasot "Pievienot moduli …"

Līdzīgi pievienojiet IP:

- HLS_Video_Track

- Video kadru buferis rakstīt

- Video rāmja bufera lasīšana

- Video laika kontrolieris

- AXI4-straume video izejai

- "Šķēle" 3.

- Pastāvīga

- 2 no AXI taimera

27. darbība: IP konfigurācijas iestatījumi

Kā parādīts attēlos

28. darbība: pievienojiet un konfigurējiet PS IP bloku

Pievienojiet ZYNQ7 apstrādes sistēmu blokshēmai

rediģējiet konfigurāciju:

- PS-PL konfigurācija

-

ZS

- Iespējot S HP 0

- Iespējot S HP 1

-

- Pulksteņa konfigurācija

-

PL Auduma pulksteņi

- FCLK_0 pie 100 MHz

- FCLK_1 pie 25 MHz (izejas pulkstenis)

- FLCK_2 pie 35 MHz (<= 50 MHz) (CameraClock)

-

29. solis: 1. daļa. PWM moduļa izveide servomotoriem

Iznesiet axi_timer_0 pwm0 uz jaunu izejas portu pwm_Xaxis

Iznesiet axi_timer_1 pwm0 uz jaunu izejas portu pwm_Zaxis

30. darbība: video ievades sānu savienojumi (iezīmēts aclk)

Pareizi pievienojiet video ieejas puses IP blokus

(* šie savienojumi jāizveido, izvēloties pareizās opcijas savienojuma automatizācijas laikā) "aclk" no axi_stream_capture iet uz:

- ap_clk par video rāmja bufera rakstīšanu

- ap_clk par HLS video straumes apstrādes bloku

- *Aclk uz AXI smartconnect IP no video kadru bufera Rakstiet uz S_AXI_HP0

- *Aclk, kas atbilst AXI Interconnect IP kanāliem HLS video apstrādes bloka S_AXI kanāliem un video rāmja buferim, PS blokā ierakstiet S_AXI_HP0_ACLK

Video straumes signāls ir vienkārši savienots virknē no uztveršanas bloka līdz Zynq atmiņas saskarnei.

- Video pāriet no uztveršanas bloka uz HLS apstrādes bloku.

- Apstrādātais video no HLS bloka nonāk kadra bufera rakstīšanas blokā.

- *Rāmja bufera rakstīšanas bloks savienojas ar HP0 saskarni Zynq PS blokā.

- M_axis_tuser signāls no uztveršanas bloka izejas tiek manuāli pieslēgts gan video ieejas signālam video_in_TUSER HLS apstrādes blokā, gan ap_start signālam tajā pašā blokā.

TUSER (tuser) signālu izmanto AXI video straumes protokols, lai norādītu video kadra sākumu. AP_Start norāda HLS blokam sākt apstrādi. Tādējādi mēs izmantojam lietotāju, lai aktivizētu HLS bloku, lai apstrādātu katru kadru tā, kā tas ir Pievienojot vienu kopnes signālu un sadalot to šādā veidā, tas ir jāpievieno arī parastajam pārējās kopnes savienojuma punktam. Vivado pieņem, ka, ja manuāli pievienojat signālu, vēlaties atvienot to, ar ko tas parasti savienotos.

IP bloku konfigurācijas iestatījumi:

Video kadra bufera rakstīšana:

Video formāti: RGB8

1 paraugs pulkstenī Maksimālās kolonnas: 1280 (> = 640) Maksimālās rindas: 960 (> = 480) Maksimālais datu platums: 8

31. darbība: savienojumi ar OV7670

Blokā ov7670_axi_stream_capture

- Padariet visas ievades ārējas (ar peles labo pogu noklikšķiniet uz tapas un atlasiet izvēlnē vai ar peles kreiso taustiņu-> ctrl+T)

- Atstājiet vārdus tādus, kādi tie ir

Ov7670_kontrollera blokā

- Padariet visas bloka izejas ārējas

- Pārdēvējiet portu config_finished uz led0

- savienot clk ar CameraClock (<= 50MHz) (FCLK_2)

Atlēcienu blokā

- pievienojiet pogu1 ieeju ārējam ievades portam ar nosaukumu btn0

- savienojiet out1 ar atkārtotas nosūtīšanas līniju ov7670_controller IP blokā

- pievienojiet pogu2 ieeju ārējam ievades portam ar nosaukumu btn3

- savienojiet out2n ar ext_reset_in ievadi procesora sistēmas atiestatīšanas IP video uztveršanas pulksteņa domēnā. (*Tas var būt jādara pēc IP ģenerēšanas*)

- savienot clk ar CameraClock (<= 50MHz) (FCLK_2)

32. darbība. Savienojumi video izejas pusē

Savienojumi blokiem Video laika kontrolieris (VTC), AXI4-Stream to Video Out un šķēles

- Izmantojiet 25MHz pulksteni (FCLK_1) vid_io_out_clk un VTC clk

- Izmantojiet 100MHz pulksteni (FCLK_0), lai skatītos AXI4-Stream uz video izeju

- vtiming_out to vtiming_in

- Video kadru buferis Lasīt m_axis_video nonāk AXI4-Stream to Video Out video_in

- vtg_ce iet uz gen_clken

- Piesaistiet VTC saspiestu, saspiestu, vid_io_out_ce ar nemainīgu dout [0: 0]

- Izvediet vid_hsync un vid_vsync attiecīgi uz ārējiem izejas portiem vga_hs un vga_vs. (nav attēlā)

Šķēles:

-

Šķēles jāiestata, kā parādīts pievienotajos attēlos

- pārdēvēt blokus uz slice_red, slice_green un slice_blue

- iestatīšanas šķēles diapazoni, kā parādīts attēlos pēc bloka nosaukuma

- savienojiet katru šķēles izvadi ar ārējo porta izeju, kā parādīts attēlā.

- vid_data [23: 0] savienojas ar katras šķēles ievadi (Din [23: 0])

33. darbība: palaidiet bloķēšanas un savienojuma automatizāciju

Palaidiet bloķēšanas automatizāciju, lai savienotu lietas no ZYNQ7 PS bloka. Kā parādīts attēlā.

Palaidiet savienojuma automatizāciju, lai izveidotu visu starpsavienojuma IP. Pievērsiet uzmanību visām iespējām katrā attēlā.

Atlēciena blokā pievienojiet out2n video uzņemšanas pulksteņa domēna procesora sistēmas atiestatīšanai ext_reset_in.

34. darbība: izveidojiet HDL iesaiņojumu

Izveidojiet HDL iesaiņojumu savam bloka dizainam.

Iestatiet to kā augšējo moduli.

35. solis: ģenerējiet bitu plūsmu, eksportējiet aparatūru uz SDK, palaidiet SDK no Vivado

Pārliecinieties, vai eksportā ir iekļauta bitu plūsma.

Bitu plūsmas ģenerēšana var aizņemt ļoti ilgu laiku.

Pēc tam palaidiet SDK

36. darbība: SDK (bez FreeRTOS)

Šī versija dara visu, neizmantojot FreeRTOS, labi kondensējot kodu.

Izveidojiet atsevišķu BSP, pamatojoties uz aparatūras dizainu. Noklusējuma opcijām vajadzētu būt labām. Pārliecinieties, vai ir izveidoti BSP avoti.

Izveidojiet lietotni, kā parādīts attēlā. (tukša lietojumprogramma)

Izdzēsiet automātiski ģenerēto galveno un importējiet pievienotos failus.

37. solis: FreeRTOS ieviešana

Šī versija izmanto FreeRTOS. Izveidojiet FreeRTOS901 BSP, pamatojoties uz aparatūras dizainu. Noklusējuma opcijām vajadzētu būt labām. Pārliecinieties, vai ir izveidoti BSP avoti.

Izveidojiet lietotni, kā parādīts attēlā. (tukša lietojumprogramma)

Izdzēsiet automātiski ģenerēto galveno un importējiet pievienotos failus.

38. solis: lietošanas instrukcijas

Šis projekts ir nedaudz grūts, lai sāktu darbu. Izpildiet norādītās darbības secībā.

Pārliecinieties, vai jūsu ZYBO neko neuzlādē, kad tas tiek ieslēgts. Tas nozīmē, ka gaismas diodei Gatavs nevajadzētu iedegties. Viens veids, kā to izdarīt, ir iestatīt sāknēšanas avota džemperi uz JTAG.

Atveriet projektu (FreeRTOS vai nē), kuru vēlaties programmēt no SDK

- Ieslēdziet ZYBO. Gaismas diodei nevajadzētu iedegties.

- Programmējiet FPGA ar bitu failu. Gaismas diodei vajadzētu iedegties. Led0 nevajadzētu iedegties.

- Palaidiet kodu (neaizmirstiet iet garām sākuma pārtraukuma punktam, ja to darāt).

Šajā brīdī jums vajadzētu iegūt izvadi VGA displejā.

Lai restartētu (ja rodas kļūdas vai kas cits): ātri pieskarieties pogai PS-SRST vai izslēdziet un pēc tam atkal ieslēdziet ZYBO. Turpiniet no 2. darbības.

Apturot procesoru ar atkļūdotāju, kamera nenotiks kustību, bet turēs pozīciju. Video straume tik un tā turpināsies.

39. darbība: atsauces un saites

Xilinx uzziņu ceļveži un dokumentācija:

- PG044 - AXI -straume video izejai

- PG278 - Video kadru buferis lasīšanai/rakstīšanai

Citas saites:

- Lauri emuārs - VDMA ievade

- Lauri emuārs - OV7670 uz VGA izvadi, izmantojot BRAM

- Hamsterworks wiki, Maiks Fīldss, OV7670 koda sākotnējais avots

- Datu lapa, kas parāda pamata laika specifikācijas

Ieteicams:

Luciferīns, bezvadu slīpuma apgaismojums jūsu datoram: 6 soļi (ar attēliem)

Luciferīns, bezvadu aizspriedumu apgaismojums jūsu datoram.: Luciferīns ir vispārējs termins gaismas izstarojošam savienojumam, kas atrodams organismos, kas rada bioluminiscenci, piemēram, Fireflies un Glow Worms. Firefly Luciferin ir Java ātrā ekrāna uztveršanas datora programmatūra, kas paredzēta Glow Worm Luciferin programmaparatūrai, tās

Pilnībā automatizēta fotografēšanas panoramēšanas iekārta: 14 soļi (ar attēliem)

Pilnībā automatizēta fotografēšanas panoramēšanas iekārta: Ievads Sveiki, šī ir mana automatizētā fotokameras panoramēšanas iekārta! Vai esat dedzīgs fotogrāfs, kurš ir vēlējies kādu no šīm patiešām foršajām automatizētajām panoramēšanas iekārtām, taču tās ir patiešām dārgas, piemēram, 350 £+ dārgas 2 asīm panoramēšana? Nu apstājies šeit

Panoramēšanas un noliekšanas mehānisms DSLR laika intervāliem: 7 soļi (ar attēliem)

Panoramēšanas un slīpuma mehānisms DSLR laika nobīdēm: man apkārt bija daži soļu motori, un es patiešām gribēju tos izmantot, lai radītu kaut ko foršu. Es nolēmu izveidot DSLR kamerai Pan and Tilt sistēmu, lai es varētu radīt lieliskus laika nobīdes. Nepieciešamās preces: 2x pakāpju motori -htt

Slīpuma slēdzis: 9 soļi (ar attēliem)

Slīpuma slēdzis: šī apmācība kalpo kā ievads mīkstajām shēmām. Izmantojot lietojumprogrammu, jūs iegūsit izpratni par elektronisko tekstilmateriālu (e-tekstila) materiālu, piemēram, vadoša auduma un vadoša diega, darba īpašībām. Konstruējot f

LED slīpuma gaismas kaste: 5 soļi (ar attēliem)

LED slīpuma gaismas kaste: šī pamācība parādīs, kā izveidot vienkāršu shēmas plati ar dzīvsudraba slēdzi (slīpuma slēdzi) un gaismas diodēm, un pēc tam nelielu koka kastīti ar logu, lai to ievietotu