Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:58.

- Pēdējoreiz modificēts 2025-06-01 06:09.

Šī ir apmācība par to, kā izveidot vienas minūtes hronometru, izmantojot VHDL un Basys 3 plāksni. Šāda ierīce ir ideāli piemērota spēlēm, kurās katram spēlētājam ir ne vairāk kā viena minūte, lai veiktu gājienu. Hronometrs septiņu segmentu displejā precīzi parāda sekundes un milisekundes, sākot no 0 sekundēm un 0 milisekundēm, līdz 60 sekundēm un 0 milisekundēm. Tiek izmantotas arī divas pogas: centrālā poga, ko izmanto, lai iedarbinātu, apturētu un turpinātu taimeri, un labā poga, ko izmanto, lai restartētu taimeri. Ja ierīci salīdzina līdzās ar viedtālruņa iebūvēto hronometru, pulksteņa precizitāte ir pamanāma.

1. darbība: iegūstiet aparatūru/programmatūru

1. Basys 3 Artix-7 FPGA treneru dēlis no Digilent ar Micro-USB līdz USB kabeli

2. Vivado 2016.2 Dizaina komplekts no Xilinx

2. darbība. Bloķēt diagrammu

Šī shēma ir veidota uzvedībā un izmanto iebūvētas Xilinx sastāvdaļas, taču to var aprakstīt arī strukturāli, kā parādīts iepriekšējā vispārējā strukturālajā diagrammā. No diagrammas redzams, ka ķēdi darbina divi frekvences dalītāji. Viens no frekvenču dalītājiem darbojas ar 1 centisekundi un vada katoda skaitītāju, kas tiek izmantoti kā septiņu segmentu displejā redzamie skaitļi. Otrais frekvences dalītājs darbojas ar frekvenci 240 Hz, un to izmanto, lai vadītu anoda skaitītāju, kas griežas caur anodiem, lai visi cipari tiktu pareizi parādīti septiņu segmentu displejā. Kodētājs ņem katoda loģiku no katoda skaitītāja un anoda loģiku no anoda skaitītāja un kodē to izejas katodā un anodā, kas vada septiņu segmentu displeju. Šī kodētāja funkcija ir katoda izejas maiņa katru reizi, kad mainās anoda izeja. Katoda izvadi nevar palaist neatkarīgi no skaitītāja, jo anodiem jāgriežas caur 4 atsevišķiem cipariem.

3. solis: projekta modulis

Pirmkārt, tiek izveidots CEN procesa bloks, lai, nosakot pogas nospiešanu, pārslēgtos ENABLE. Tas kalpo kā katoda skaitītāja apturēšana/sākšana.

Nākamajā procesa blokā centisekundes un 240 Hz pulksteņa signāli tiek iestatīti tā, ka to skaitītāji palielinās par 1 katru reizi, kad iekšējais 100 MHz pulkstenis sasniedz pieaugošo malu. Kad centisekundes skaitītājs sasniedz 500000, tas tiek atiestatīts uz 0. Tikmēr 240 Hz skaitītājs tiks atiestatīts, kad skaitlis sasniegs 41667.

Koda katoda sadaļā, ja ENABLE ir “0”, katoda skaitīšana tiks apturēta. Ja šajā laikā tiek nospiesta atiestatīšanas poga, tad visi skaitļi tiek atiestatīti uz "0000". Tikmēr, ja ENABLE ir “1”, katoda skaitīšana turpināsies, līdz katodu skaits sasniegs 60.00, un tas aktivizēs apstāšanās signālu kā “1”. Apturēšanas signāls tiek novirzīts atpakaļ uz CEN procesa bloku un liek ENABLE būt '0', kamēr apstāšanās signāls ir '1' un nemainās, kamēr nav nospiesta atiestatīšanas poga.

Visbeidzot, septiņu segmentu displejs ir iestatīts, ja 4 anodi ir pareizi savienoti ar katru no katodiem, lai vienlaikus parādītu attiecīgos ciparus 0-9.

4. solis: ierobežojumi

Šis ierobežojumu fails savieno norādītās VHDL ieejas un izejas ar nepieciešamajām Basys paneļa fiziskajām daļām. Šim projektam komponenti ietver četrus anodus un katru no astoņiem katodiem septiņu segmentu displejam, iekšējo 100 mHz pulksteni, centrālo pogu un labo pogu.

5. solis: pārbaudiet

Kad esat pabeidzis kodu, tagad varat programmēt FPGA, izmantojot USB kabeli. Septiņu segmentu displejā vajadzētu parādīt 0,00. Pārbaudiet, vai pogas darbojas, nospiežot centrālo pogu, lai iedarbinātu taimeri, līdz tas sasniedz 60.00 un apstājas; jebkurā laikā varat vēlreiz nospiest centrālo pogu, lai to apturētu. Kad tas ir apturēts, varat nospiest labo pogu, lai atjaunotu taimeri uz 0.00. Ja viss darbojas pareizi, apsveicam, ka tikko izveidojāt vienas minūtes taimeri!

Ieteicams:

Arduino Leonardo hronometrs: 3 soļi

Arduino Leonardo hronometrs: Kredīts: https://www.instructables.com/id/Arduino-Stopwatch … Šis hronometra dizains radās no iepriekš minētās saites, kas ir hronometrs, kas skaitās no 1, turpretim šis skaitās no 60 sekundēm . Lielākā daļa izmantotā koda atbilst oriģinālam

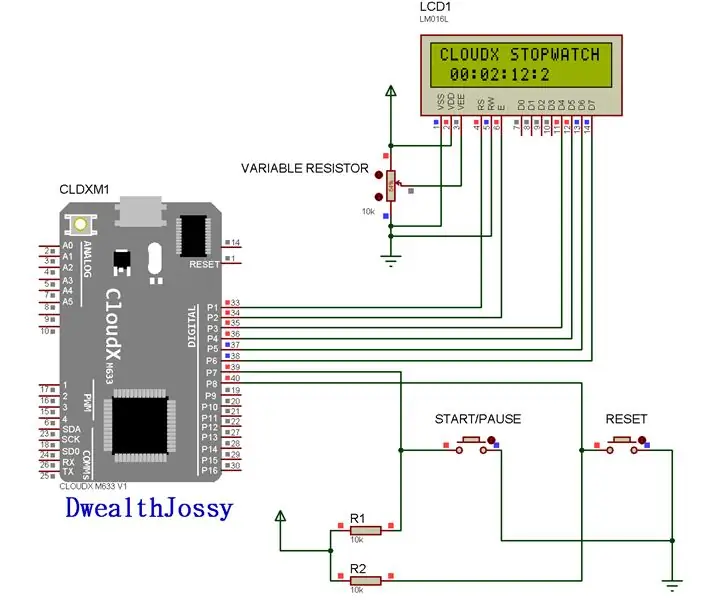

Vienkāršs CloudX M633 digitālais hronometrs: 4 soļi

Vienkāršs CloudX M633 digitālais hronometrs: šajā projektā mēs izveidosim digitālā pulksteņa versiju, kas var saglabāt stundu, minūšu un sekunžu ierakstu, tāpat kā hronometrs jūsu mobilajā tālrunī! Mēs izmantosim LCD, lai parādītu laiku

Croakers hronometrs: 16 soļi (ar attēliem)

Krokera hronometrs: ja jūs smaidīsit vardēm, dažas no tām vibrēs. Izprotot kustību, var pateikt laiku-trīcošu darbību.Vardes " skatoties uz augšu " attēlo stundas binārā formātā (no kreisās uz labo; 8,4,2,1). Vardes " gaida uz priekšu " pārstāvēt min

Pamata hronometrs, izmantojot VHDL un Basys3 Board: 9 soļi

Pamata hronometrs, izmantojot VHDL un Basys3 Board: Laipni lūdzam pamācībā, kā izveidot hronometru, izmantojot pamata VHDL un Basys 3 plates. Mēs esam priecīgi dalīties ar jums mūsu projektā! Šis bija pēdējais projekts kursam CPE 133 (digitālais dizains) Cal Poly, SLO 2016. gada rudenī. Projekts, kuru mēs veidojam

VHDL hronometrs: 8 soļi (ar attēliem)

VHDL hronometrs: šī ir apmācība, kā izveidot hronometru, izmantojot VHDL un FPGA shēmas plati, piemēram, Basys3 Atrix-7 plati. Hronometrs spēj skaitīt no 00.00 sekundēm līdz 99.99 sekundēm. Tas izmanto divas pogas, vienu start/stop pogai un otru