Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:56.

- Pēdējoreiz modificēts 2025-01-23 14:59.

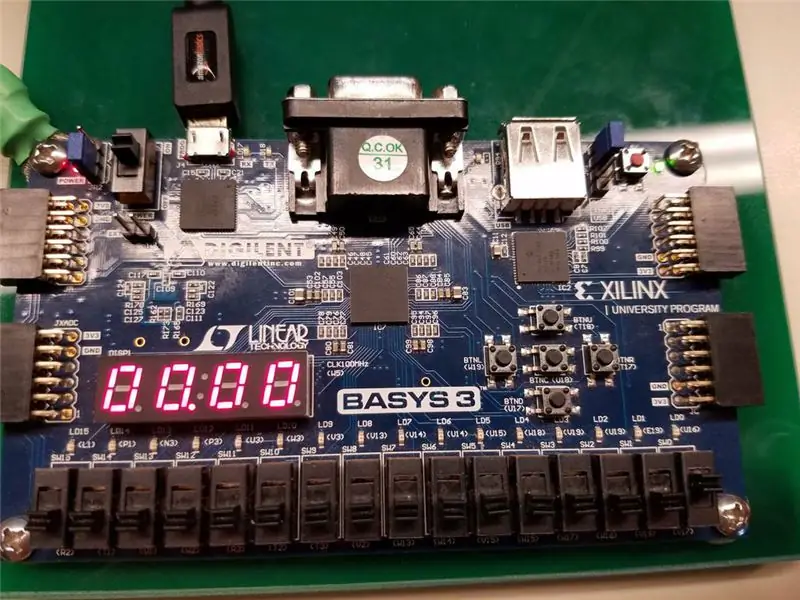

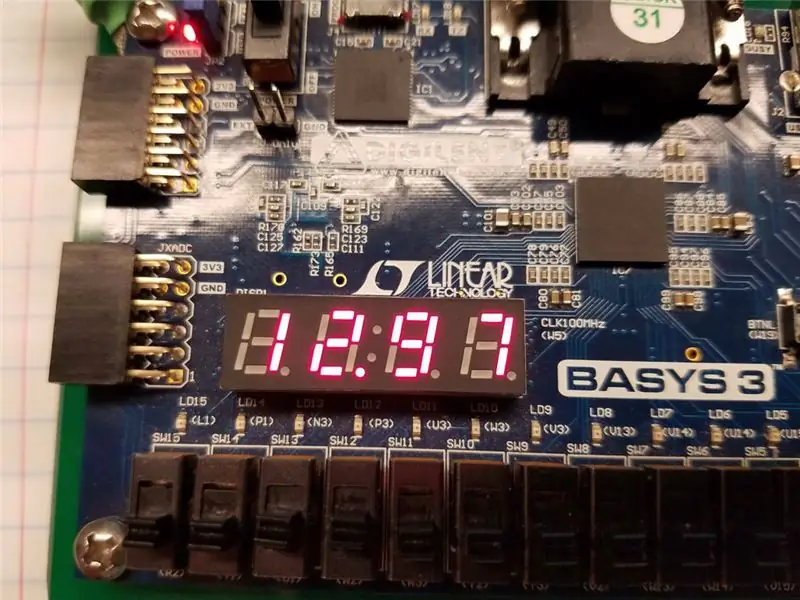

Laipni lūdzam pamācībā, kā izveidot hronometru, izmantojot pamata VHDL un Basys 3 plates. Mēs esam priecīgi dalīties ar jums mūsu projektā! Šis bija pēdējais projekts kursam CPE 133 (digitālais dizains) Cal Poly, SLO 2016. gada rudenī. Mūsu izveidotais projekts ir vienkāršs hronometrs, kas iedarbina, atiestata un aptur laiku. Kā ieejas tiek izmantotas trīs spiedpogas uz Basys3 tāfeles, un laiks tiek parādīts tāfeles četru ciparu septiņu segmentu displejā. Pagājušais laiks tiek parādīts sekundēs: centisekundes formātā. Tas izmanto paneļa sistēmas pulksteni kā ievadi, lai izsekotu pagājušajam laikam, un izvada laiku septiņu segmentu displeja četriem cipariem.

1. solis: materiāli

Šim projektam būs nepieciešami materiāli:

- 1 dators ar Vivado Design Suite WebPack, kas instalēts no Xilinx (dod priekšroku versijai 2016.2)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA plate

- 1 USB porta kabelis

2. darbība: ievades un izejas iestatīšana

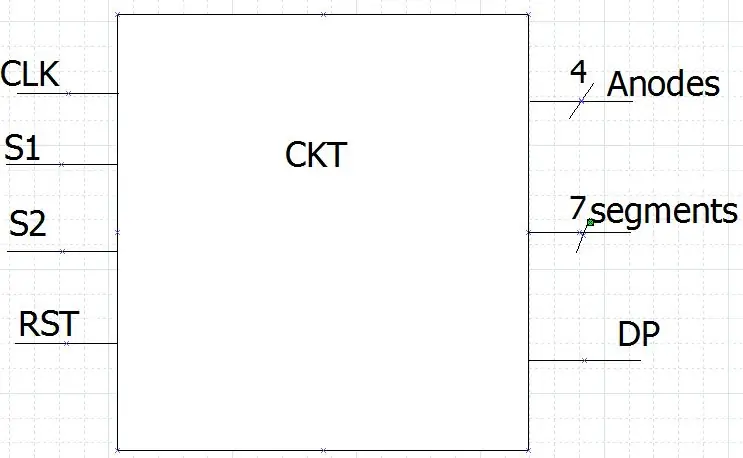

Iepriekš redzamajā attēlā redzama galvenā hronometra moduļa augšējā līmeņa blokshēma. Hronometrs ievada ieejas "CLK" (pulkstenis), "S1" (sākuma poga), "S2" (pauzes poga) un "RST" (atiestatīšana), un tam ir 4 bitu izeja "Anodes", 7 bitu izvade "segments" un viena bita izeja "DP" (aiz komata). Ja ievade "S1" ir augsta, hronometrs sāk skaitīt laiku. Kad "S2" ir zems, hronometrs aptur laiku. Kad "RST" ir augsts, hronometrs apstājas un atiestata laiku. Ķēdē ir četri apakšmoduļi: pulksteņa dalītājs, ciparu skaitītājs, septiņu segmentu displeja draiveris un septiņu segmentu displeja kodētājs. Hronometra galvenais modulis savieno visus apakšmoduļus kopā ar ieejām un izejām.

3. solis: pulksteņu izgatavošana

Pulksteņa dalītāja modulis uzņem sistēmas pulksteni un izmanto dalītāja ievadi, lai izveidotu pulksteņa ātrumu, kas nav lielāks par sistēmas pulksteņa ātrumu. Hronometrs izmanto divus dažādus pulksteņa moduļus, no kuriem viens rada 500 Hz pulksteni, bet otrs - 100 Hz pulksteni. Pulksteņa dalītāja shēma ir parādīta attēlā iepriekš. Pulksteņa dalītājs uzņem viena bita ievadi "CLK" un 32 bitu ieeju "dalītājs" un viena bita izeju "CLKOUT". "CLK" ir sistēmas pulkstenis, un "CLKOUT" ir iegūtais pulkstenis. Modulis ietver arī NOT vārtus, kas pārslēdz signālu "CLKTOG", kad skaitlis sasniedz dalītāja vērtību.

4. solis: skaitīšana līdz desmit

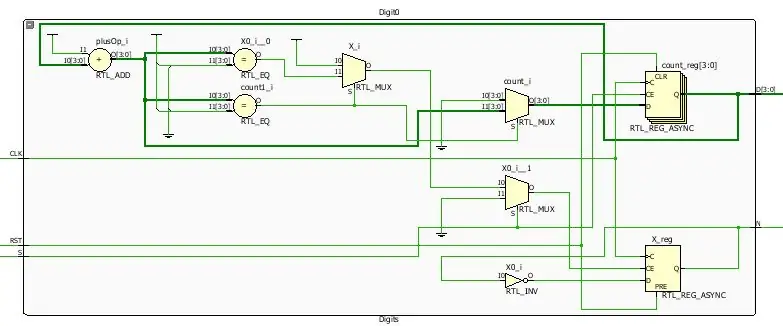

Ciparu skaitītājs saskaita katru ciparu no 0 līdz 10 un izveido citu pulksteni, lai nākamais cipars darbotos, un tas svārstās, kad skaitlis sasniedz 10. Modulis uzņem 3 viena bita ievades "S", "RST" un "CLK" "un iegūst viena bita izvadi" N "un 4 bitu izvadi" D ". Ievads "S" ir iespējošanas ievade. Pulkstenis ieslēdzas, kad “S” ir augsts, un izslēdzas, kad “S” ir zems. "RST" ir atiestatīšanas ievade, tāpēc pulkstenis tiek atiestatīts, kad "RST" ir augsts. "CLK" ir ciparu skaitītāja pulksteņa ievade. "N" ir pulksteņa izeja, kas kļūst par nākamā cipara ievades pulksteni. Izvade "D" parāda skaitļa bināro vērtību, pie kuras atrodas skaitītājs.

5. darbība: ciparu parādīšana

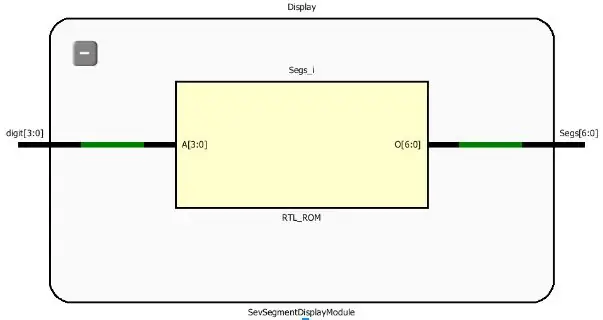

Septiņu segmentu displeja kodētājs kodēs no septiņu segmentu displeja draivera moduļa saņemto bināro skaitli un pārvērtīs to bitu plūsmā, kas tiks interpretēta kā “1” vai “0” vērtības katram displeja segmentam. Bināro skaitli modulis saņem kā 4 bitu ievades "ciparu" un iegūst 7 bitu izejas "segmentus". Modulis sastāv no viena gadījuma procesa bloka, kas katrai iespējamai ievades vērtībai no 0 līdz 9. piešķir noteiktu 7 bitu straumi. Katrs bits septiņu bitu straumēs attēlo vienu no septiņiem displeja ciparu segmentiem. Straumē esošo segmentu secība ir “abcdefg”, un “0” apzīmē segmentus, kas iedegas konkrētajam skaitlim.

6. darbība. Hronometra parādīšana

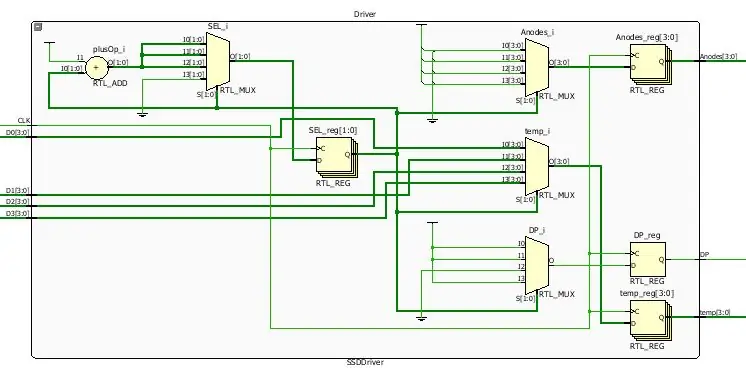

Septiņu segmentu displeja draivera modulī ir četras 4 bitu ieejas "D0", "D1", "D2" un "D3", katra no tām attēlo četrus ciparus. Ievade "CLK" ir sistēmas pulksteņa ievade. Viena bita izvade "DP" apzīmē decimāldaļu septiņu segmentu displejā. 4 bitu izeja "Anodes" nosaka, kurš cipars septiņu segmentu displejā tiek parādīts, un 4 bitu izeja "temp" ir atkarīga no 2 bitu vadības ievades "SEL" stāvokļa. Modulis izmanto 4 multipleksorus vadības ieejai "SEL" un trim izejām; "Anodi", "temp" un "DP".

7. solis: apvienojiet to visu

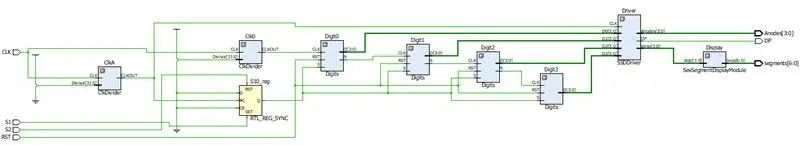

Sākuma un pauzes pogu izveidei tiek izmantots procesa bloks, kas darbojas no 500 Hz pulksteņa. Pēc tam savienojiet visus apakšmodulus hronometra galvenajā modulī, deklarējot katra atsevišķa apakšmoduļa komponentus un izmantojot dažādus signālus. Ciparu apakšmoduļi uzņem iepriekšējā ciparu apakšmoduļa pulksteņa izeju, bet pirmais - 100 Hz pulksteni. Pēc tam ciparu apakšmoduļu "D" izejas kļūst par septiņu segmentu displeja draivera moduļa "D" ieejām. Visbeidzot, septiņu segmentu displeja draivera moduļa "temp" izvade kļūst par septiņu segmentu kodētāja moduļa "temp" ievadi.

8. solis: ierobežojumi

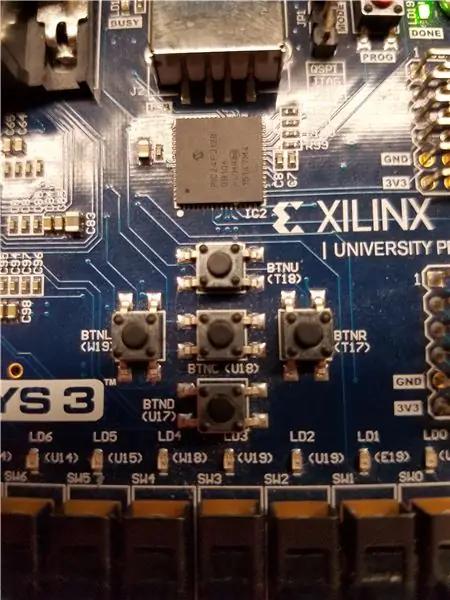

Ievadiem "RST", "S1" un "S2" izmantojiet 3 spiedpogas (W19, T17 un U18). W19 ir atiestatīšanas poga, T17 ir sākuma poga (S1), bet U18 ir pauzes poga (S2). Pulksteņa ievades ierobežojums ir nepieciešams arī, izmantojot portu W5. Atcerieties arī pievienot šo rindu pulksteņa ierobežojumam:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Arī saistiet anodus un segmentus ar tāfeli, lai hronometrs tiktu parādīts septiņu segmentu displejā, kā redzams ierobežojumu failā.

9. solis: pārbaude

Pārliecinieties, vai jūsu ierīce darbojas, spēlējot ar trim pogām: nospiežot un turot tās visos iespējamos secībā, lai atrastu iespējamās problēmas ar kodu.

Ieteicams:

Kā izveidot pamata vietni, izmantojot Notepad: 4 soļi

Kā izveidot pamata vietni, izmantojot piezīmjdatoru: Vai kāds ir prātojis, "kā es varu izveidot vietni no pamata rakstīšanas programmas?" "Nu, acīmredzot, ne īpaši … Jebkurā gadījumā, šeit es jums parādīšu, kā izveidot BASIC vietne, izmantojot tikai piezīmju grāmatiņu

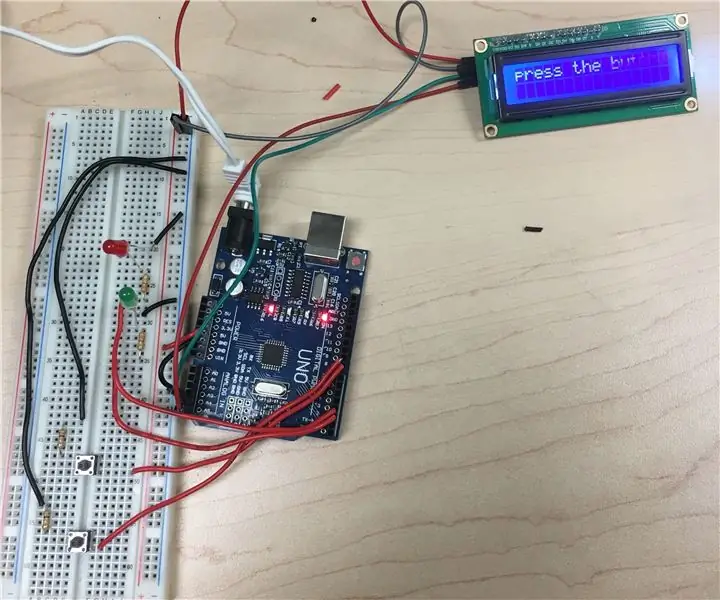

Arduino hronometrs, izmantojot I2C LCD: 5 soļi

Arduino hronometrs, izmantojot I2C LCD: Šajā projektā es iemācīšu jums izmantot LCD displeju un Arduino kā interaktīvu hronometru. Kad jūsu projekts ir pabeigts, izmantojot norādīto kodu, tam vajadzētu izskatīties kā iepriekš redzamajā fotoattēlā. Dodieties uz nākamo soli, lai uzzinātu, kur sākt

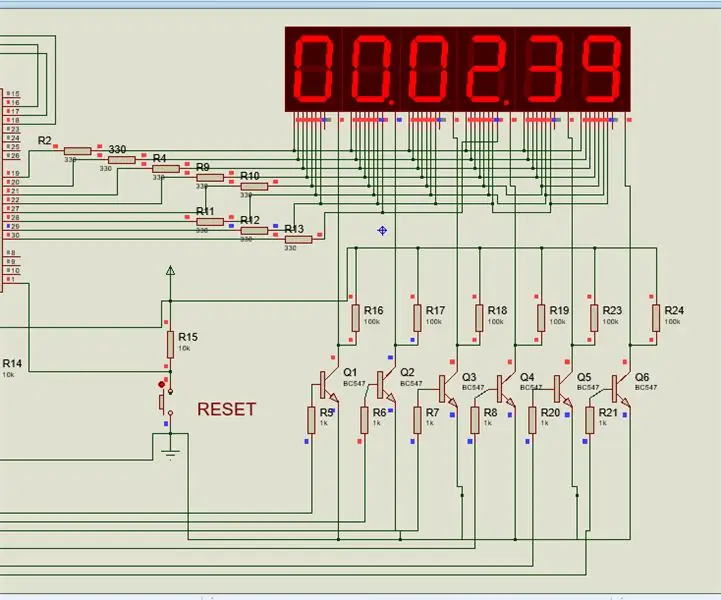

Hronometrs, izmantojot Pic18f4520 programmā Proteus ar 7 segmentiem: 6 soļi

Hronometrs Izmantojot Pic18f4520 programmā Proteus ar 7 segmentu: es tikko sāku strādāt ar attēlu kontrolieri, viens no maniem draugiem lūdza no tā izveidot hronometru. Tāpēc man nav aparatūras attēla, ar ko dalīties, esmu uzrakstījis kodu un simulējis to Proteus programmatūrā. Šeit es esmu kopīgojis tā paša shēmu. T

VHDL vienas minūtes hronometrs: 5 soļi

VHDL vienas minūtes hronometrs: šī ir apmācība, kā izveidot vienas minūtes hronometru, izmantojot VHDL un Basys 3 plāksni. Šāda ierīce ir ideāli piemērota spēlēm, kurās katram spēlētājam ir ne vairāk kā viena minūte, lai veiktu gājienu. Hronometrs precīzi parāda sekundes un milisekundes

VHDL hronometrs: 8 soļi (ar attēliem)

VHDL hronometrs: šī ir apmācība, kā izveidot hronometru, izmantojot VHDL un FPGA shēmas plati, piemēram, Basys3 Atrix-7 plati. Hronometrs spēj skaitīt no 00.00 sekundēm līdz 99.99 sekundēm. Tas izmanto divas pogas, vienu start/stop pogai un otru