Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:58.

- Pēdējoreiz modificēts 2025-01-23 14:59.

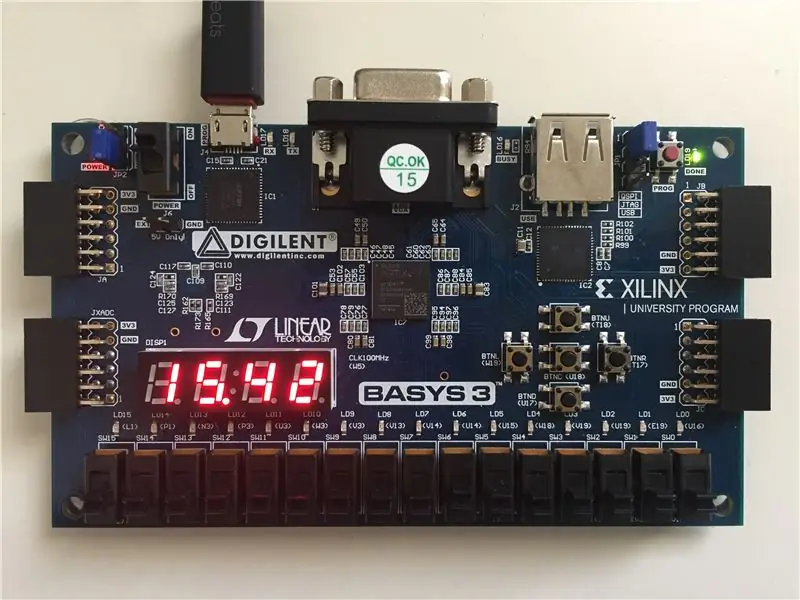

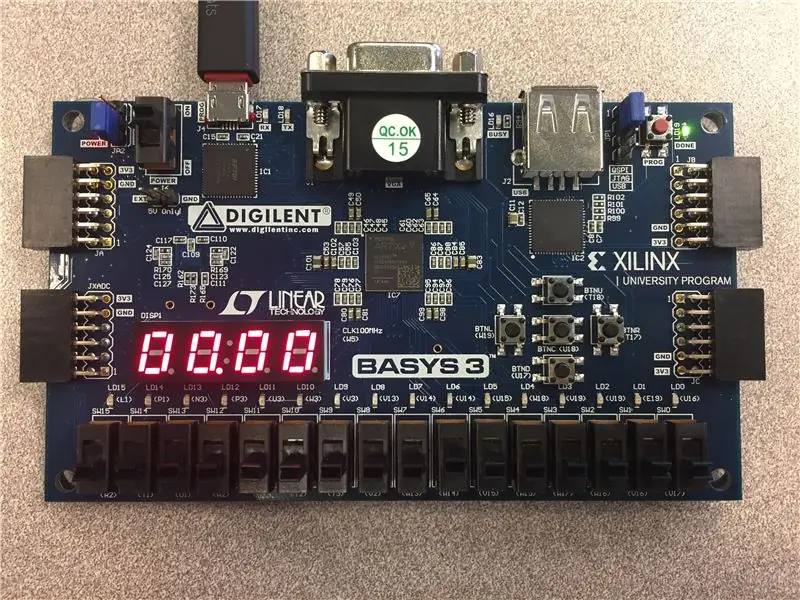

Šī ir apmācība, kā izveidot hronometru, izmantojot VHDL un FPGA shēmas plati, piemēram, Basys3 Atrix-7 plati. Hronometrs spēj skaitīt no 00.00 sekundēm līdz 99.99 sekundēm. Tas izmanto divas pogas, vienu start/stop pogai un otru atiestatīšanas pogai. Skaitļi tiek parādīti tāfeles septiņu segmentu displejā, izmantojot tā anodus un katodus. Lai šis hronometrs darbotos, nepieciešami trīs dažādi faili.

1. darbība: aparatūra/programmatūra

- Basys3 Atrix-7 FPGA plate

- Vivado dizaina komplekts no Xilinx

- USB 2.0 no vīrieša līdz Micro-B vīrietim

2. darbība. Bloķēt diagrammu

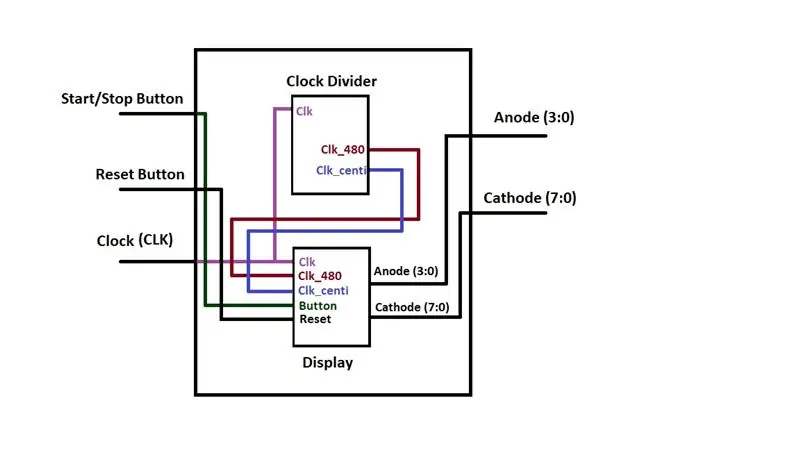

Kopējam hronometram ir trīs ieejas un divas izejas. Trīs ieejas ir start/stop, reset un pulkstenis. Sākt/apturēt un atiestatīt ir pogas, un pulkstenis ir tāfeles 100MHz pulkstenis. Divas izejas ir septiņu segmentu displeja anodi un katodi.

Pirmajam modulim (pulksteņa dalītājam) ir viena ieeja un divas izejas. Ieeja ir 100MHz pulksteņa pulkstenis, un izejas ir divi atsevišķi pulksteņi, no kuriem viens darbojas 480Hz un otrs - 0,5MHz.

Otrajam modulim (displejam) ir piecas ieejas un divas izejas. Ievadi ir tāfeles 100MHz pulkstenis, divi pulksteņi no pulksteņa dalītāja moduļa un start/stop un reset pogas. Izejas ir anodi un katodi.

Pēdējam modulim (modelēts pēc visas blokshēmas) ir trīs ieejas un divas izejas. Šis ir fails, kas apvieno visu. Ieejas ir plates 100MHz un start/stop un reset pogas. Izejas ir anodi un katodi, kas kontrolē septiņu segmentu displeju. Visas ieejas un izejas fiziski atrodas gala moduļa panelī.

3. darbība: valsts diagramma

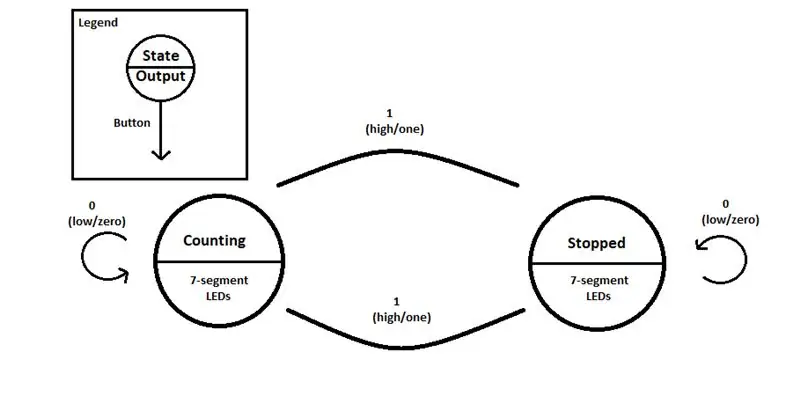

Augšējā attēlā parādīta hronometra darbības stāvokļa diagramma. Atiestatīšanas pogas nospiešana neietekmē hronometra stāvokli. Nākamo stāvokli nosaka start/stop poga. Sākums/apturēšana ir "HIGH", nospiežot uz leju, bet ne tad, kad tas ir nospiests, un "LOW", ja poga ir atgriezusies atpakaļ vai tiek turēta nospiesta pēc tam, kad ir bijusi "HIGH".

Ja hronometrs sāk skaitīt un start/stop poga ir "HIGH", tad skaitīšana tiek pārtraukta. Ja hronometrs ir apturēts un start/stop poga ir "HIGH", tad tas sāk skaitīt no jauna. Abās valstīs, ja start/stop poga ir "LOW", tā paliks tādā stāvoklī, kādā tā pašlaik atrodas.

4. solis: pulksteņa dalītāja modulis

Pulksteņa dalītāja modulim ir viena ieeja, 100MHz pulksteņa pulkstenis un divas izejas - 480Hz un 0,5MHz pulksteņi. 480 Hz pulkstenis tiek izmantots, lai visas septiņu segmentu displeja gaismas diodes būtu "ieslēgtas" vienlaicīgi, ātri pārslēdzoties pa četriem. 0,5MHz pulkstenis tiek izmantots, lai hronometrs faktiski skaitītu par centi sekundēm.

5. darbība: displeja modulis

Šim displeja modulim ir piecas ieejas, tāfeles 100MHz pulkstenis, divi pulksteņi no pulksteņa moduļa, start/stop un reset pogas, kā arī divas izejas - anodi un katodi. Šim modulim ir arī "loģika" hronometra skaitīšanai un galīgā stāvokļa mašīnas iekļaušanai.

6. solis: Iesiešanas modulis

Šis pēdējais modulis apvieno pārējos divus moduļus. Tam ir trīs ieejas, plates 100MHz pulkstenis un start/stop un reset pogas, un divas izejas - anodi un katodi. 100MHz pulkstenis iet uz pulksteņa dalītāja moduli un displeja moduli, un start/stop un reset pogas - uz displeja moduli. Pulksteņa dalītāja moduļa izejas (480Hz un 0,5MHz) nonāk displeja moduļa divās pulksteņa ieejās. Displeja moduļa izejas (anodi un katodi) nonāk gala moduļa izejās.

7. solis: ierobežojumi

Abas ieejas var būt jebkuras pogas Basys3 Atrix-7 FPGA panelī, un izejas būs četri anodi un astoņi katodi (jo vēlaties arī decimālzīmi starp sekundēm un milisekundēm) septiņu segmentu displejam.

8. solis: Gatavs

Augšupielādējiet programmu savā Basys3 Atrix-7 FPGA panelī un nospiediet start/stop pogu, lai hronometrs darbotos!

Ieteicams:

Croakers hronometrs: 16 soļi (ar attēliem)

Krokera hronometrs: ja jūs smaidīsit vardēm, dažas no tām vibrēs. Izprotot kustību, var pateikt laiku-trīcošu darbību.Vardes " skatoties uz augšu " attēlo stundas binārā formātā (no kreisās uz labo; 8,4,2,1). Vardes " gaida uz priekšu " pārstāvēt min

Viss vienā digitālais hronometrs (pulkstenis, taimeris, modinātājs, temperatūra): 10 soļi (ar attēliem)

Viss vienā digitālais hronometrs (pulkstenis, taimeris, modinātājs, temperatūra): mēs plānojām izveidot taimeri kādām citām sacensībām, bet vēlāk mēs ieviesām arī pulksteni (bez RTC). Sākot programmēšanu, mūs interesēja vairāk ierīču funkciju pielietošana un galu galā pievienojām DS3231 RTC, jo

Pamata hronometrs, izmantojot VHDL un Basys3 Board: 9 soļi

Pamata hronometrs, izmantojot VHDL un Basys3 Board: Laipni lūdzam pamācībā, kā izveidot hronometru, izmantojot pamata VHDL un Basys 3 plates. Mēs esam priecīgi dalīties ar jums mūsu projektā! Šis bija pēdējais projekts kursam CPE 133 (digitālais dizains) Cal Poly, SLO 2016. gada rudenī. Projekts, kuru mēs veidojam

Arduino hronometrs: 4 soļi (ar attēliem)

Arduino hronometrs: šī pamācība parādīs, kā no Arduino izveidot hronometru

VHDL vienas minūtes hronometrs: 5 soļi

VHDL vienas minūtes hronometrs: šī ir apmācība, kā izveidot vienas minūtes hronometru, izmantojot VHDL un Basys 3 plāksni. Šāda ierīce ir ideāli piemērota spēlēm, kurās katram spēlētājam ir ne vairāk kā viena minūte, lai veiktu gājienu. Hronometrs precīzi parāda sekundes un milisekundes