Satura rādītājs:

- Autors John Day day@howwhatproduce.com.

- Public 2024-01-30 10:51.

- Pēdējoreiz modificēts 2025-01-23 14:59.

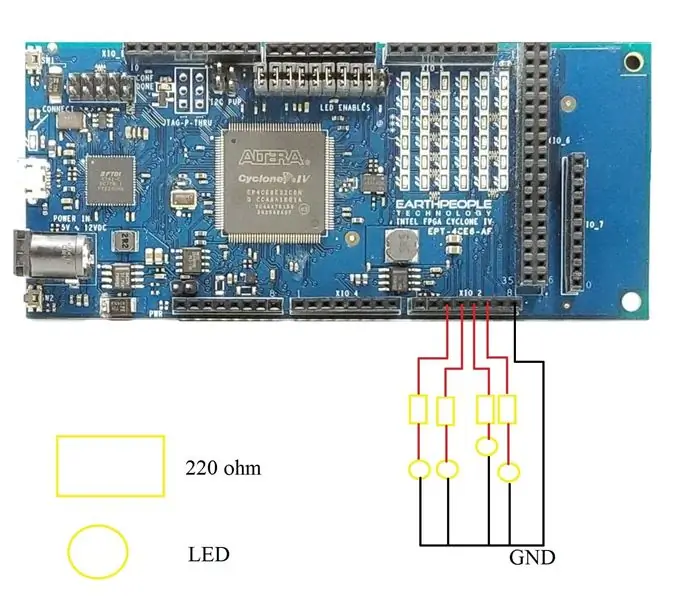

Šajā apmācībā mēs izmantosim FPGA, lai kontrolētu ārējo LED ķēdi. Mēs īstenosim šādus uzdevumus

(A) Izmantojiet FPGA Cyclone IV DuePrologic spiedpogas, lai kontrolētu LED.

(B) Zibspuldzes gaismas diode periodiski ieslēdzas un izslēdzas

Video demonstrācija

Laboratorijas izvēlne:

1. darbība: izveidojiet elektronisko shēmu

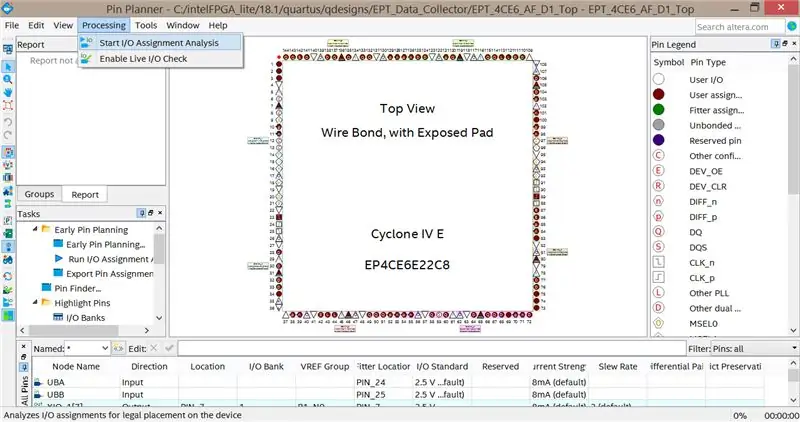

2. darbība. Pārbaudiet Pin Planner un rediģējiet Verilog kodu

3. darbība: rediģējiet Verilog kodu

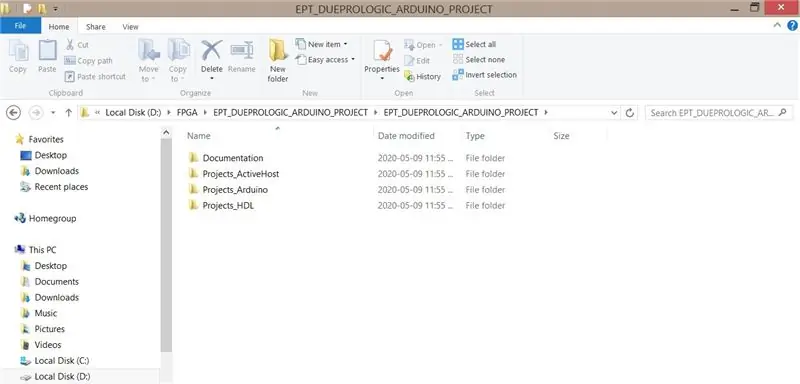

Pērkot FPGA DueProLogic, jums jāsaņem DVD. Pēc “Projects_HDL” atvēršanas jums vajadzētu redzēt sākotnējo koda failu

Pievienojiet iezīmēto kodu. Tas reģistrē I/O portus un piešķir portiem numurus.

izejas vads [7: 0] XIO_1, // XIO-D2-D9

izejas vads [5: 0] XIO_2, // XIO-D10-D12

izejas vads [5: 0] XIO_3, // XIO-D22-D29

ievades vads [5: 0] XIO_4, // XIO-D30-D37

ievades vads [5: 0] XIO_5, // XIO-D38-D45

izejas vads [4: 0] XIO_6_OUT, // XIO-D46-D53

ievades vads [31: 5] XIO_6, // XIO-D46-D53

izejas vads [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

ievades vads UBA, // spiedpogu slēdži

ievades vads UBB // spiedpogu slēdži

piešķirt XIO_1 [3] = start_stop_cntrl;

piešķirt XIO_2 [1] = start_blinky; // LED zibspuldzes LED ieslēgšana un izslēgšana

piešķirt XIO_2 [2] = 1'b1; // izvade HIGH

piešķirt XIO_2 [3] = ~ UBA; // Nospiediet pogu A

piešķirt XIO_2 [4] = UBB; // Nospiediet pogu B

piešķirt c_enable = XIO_5 [2];

piešķirt LEDExt = XIO_5 [5];

Tad mums ir jāiestata aiztures taimeris. Komentējiet sākotnējo taimera kodu un uzrakstiet jaunu taimera funkciju

//-----------------------------------------------

// LED Blinky start

//-----------------------------------------------

/*

vienmēr @(pozingge CLK_66 or negedge RST)

sākt

ja (! RST)

start_blinky <= 1'b0;

citādi

sākt

ja (kontroles_reģistrācija [7: 4]> 0)

start_blinky <= 1'b1;

citādi

start_blinky <= 1'b0;

beigas

beigas

*/

reg [31: 0] ex;

sākotnējais sākums

ex <= 32'b0;

start_blinky <= 1'b0;

beigas

vienmēr @(pozācija CLK_66)

sākt

ex <= ex + 1'b1;

ja (ex> 100000000) // zibspuldze ieslēgta/izslēgta ~ 1,6 sekundes, pulkstenis 66 MHz

sākt

start_blinky <=! start_blinky;

ex <= 32'b0;

beigas

beigas

//-----------------------------------------------

// LED aizkaves taimera skaitītājs

//-----------------------------------------------

/*

vienmēr @(pozingge CLK_66 or negedge RST)

sākt

ja (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

citādi

sākt

ja (norādiet [SELECT_MODE])

led_delay_counter <= taimera_vērtība;

cits ja (norādīt [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

beigas

beigas*/

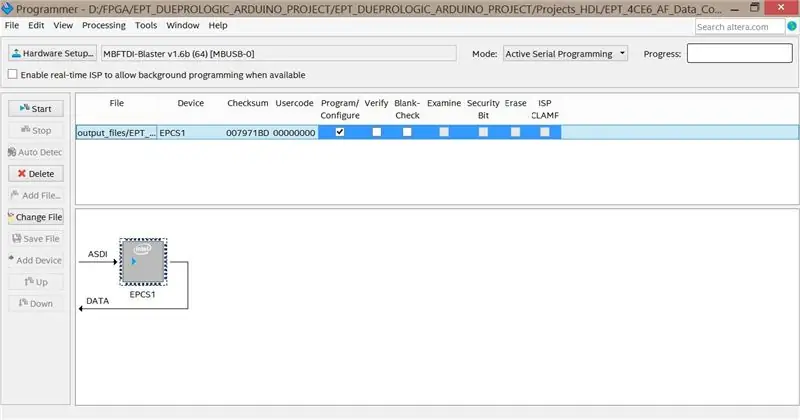

4. darbība: apkopojiet Verilog kodu

Quartus nospiediet "Sākt apkopošanu", nevajadzētu ģenerēt kļūdas ziņojumu.

Ja tiek parādīts kļūdas ziņojums par vairākām tapām. Dodieties uz Uzdevumi -> Ierīce -> Ierīces un tapas opcijas -> Divējāda mērķa tapas -> mainiet atbilstošās tapas vērtību uz "Lietot kā regulāru I/O".

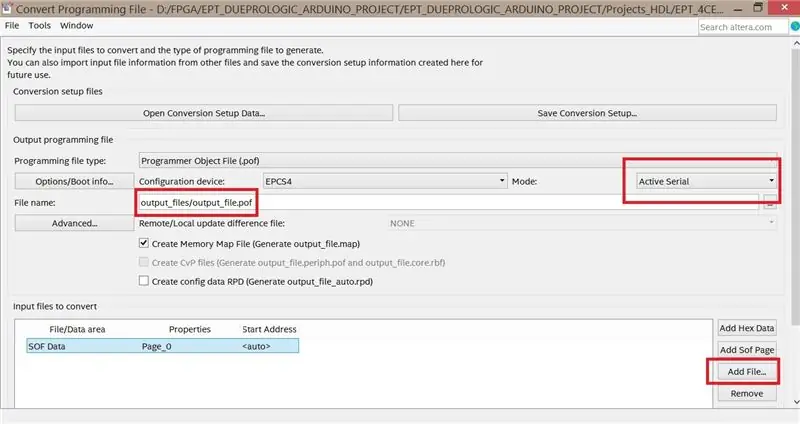

Pēc apkopošanas jums tieši jāsaņem pof izvades fails. Ja jūsu programmatūra nav atjaunināta, jūs varat iegūt tikai sof failu. Kad tas notiek, Quartus noklikšķiniet uz "Fails" -> "konvertēt programmēšanas failus". Mainiet iestatījumus, kas atzīmēti ar sarkanām rūtiņām.

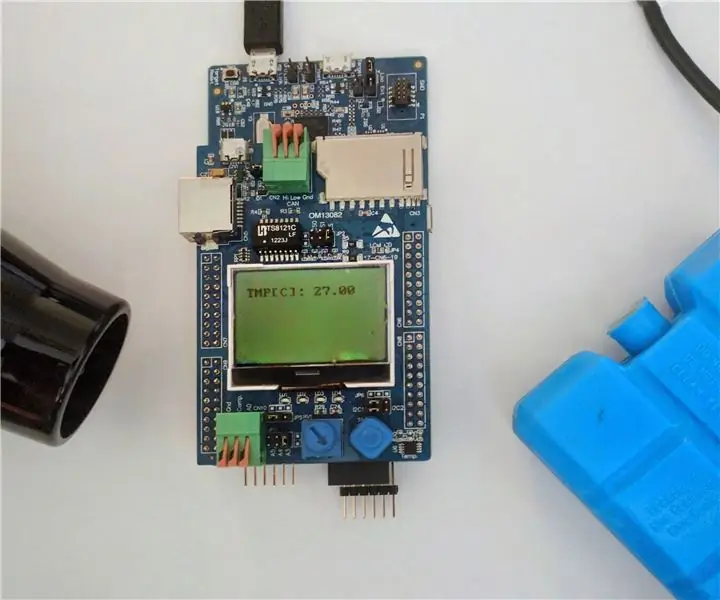

5. darbība: izmēģināsim

Galu galā tam vajadzētu strādāt !!! Dzeltenā gaismas diode vienmēr deg. Mirgo sarkanā gaismas diode. Zilā gaismas diode tiek izslēgta, nospiežot pogu B. Zaļā gaismas diode iedegas, nospiežot pogu A.

Ieteicams:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi kamera: 5 soļi

FPGA Cyclone IV DueProLogic Controls Raspberry Pi kamera: Neskatoties uz FPGA DueProLogic ir oficiāli izstrādāta Arduino, mēs padarīsim FPGA un Raspberry Pi 4B sazināmus. Šajā apmācībā ir īstenoti trīs uzdevumi: (A) Vienlaicīgi nospiediet divas spiedpogas FPGA, lai pagrieztu leņķi

FPGA Cyclone IV DueProLogic Controls Servo motors: 4 soļi

FPGA Cyclone IV DueProLogic Controls Servo Motor: Šajā apmācībā mēs rakstīsim Verilog kodu, lai kontrolētu servomotoru. Servo SG-90 ražo Waveshare. Pērkot servomotoru, jūs varat saņemt datu lapu, kurā uzskaitīts darba spriegums, maksimālais griezes moments un ierosinātā

DIY VR skrejceļš- Basys3 FPGA-Digilent konkurss: 3 soļi

DIY VR skrejceļš- Basys3 FPGA-Digilent konkurss: Vai vēlaties izveidot VR skrejceliņu, kurā varētu darbināt darbvirsmas lietojumprogrammas un spēles? Tad jūs esat nonācis īstajā vietā! Parastajās spēlēs jūs izmantojat peli un tastatūru, lai mijiedarbotos ar vidi. Tāpēc mums ir jānosūta

Mojo FPGA attīstības padomes vairogs: 3 soļi

Mojo FPGA attīstības paneļa vairogs: savienojiet savu Mojo izstrādes paneli ar ārējām ieejām, izmantojot šo vairogu. Kas ir Mojo izstrādes dēlis? Mojo izstrādes dēlis ir izstrādes dēlis, kura pamatā ir Xilinx spartan 3 FPGA. Dēlis ir izgatavots Alchitry. FPGA ir ļoti noderīgi

Izveidojiet jebkuru sensoru no FPGA: 4 soļi

Izveidojiet jebkuru sensoru no FPGA: Lielākā daļa ražotāju vismaz vienu reizi mūžā mēģināja izveidot termometru, varbūt mājās esošais nav pietiekami gudrs, vai varbūt domā, ka var uzbūvēt nākamo NEST. Tomēr kādā brīdī viņiem bija mikrokontrolleris ar savu stāvokli